# MEDIATER Distinguished Lecture

# 19 February 2016 10:30 am

# Understanding Self-timed Circuits

# Drs Ivan Sutherland & Marly Roncken Turing Laureate Kyoto Laureate

(Computer Science 'Nobel Prize')

Nearly all modern digital computers march to the beat of a "clock." The computer clock divides each second into a few billion "clock periods" just as a school bell divides each day into fixed-length class periods. A 55-minute class period is so useful for scheduling students and classrooms that educators rarely ask if it is best for learning. In reality, 55 minutes is either too short or too long.

We are one of a few research groups who study how to replace the rigid clock with more flexible "self-timed" regimes. Self-timed systems allow each small task to take its own natural time just as "self-paced" learning allows each student to learn at his or her own natural pace. Easy tasks finish quickly and take little energy. Difficult tasks require more time and energy.

In operation, a self-timed system is as orderly as a kindergarten playground at recess. Marly and Ivan will show how the parts of such a system interact, and how they can be tested. Venue: Executive Seminar Room (S2.2-B2-53)

**Great insights from**

The 'Asynchronous Duo': Pioneers of Self-Timed Logic

Friday 19 February, 2016 10:30 am – 12:30 pm

> Refreshments Provided

RSVP to virtus@pmail.ntu.edu.sg by 10 February, 2016

### Organized by ViRTUS - IC Design Centre of Excellence

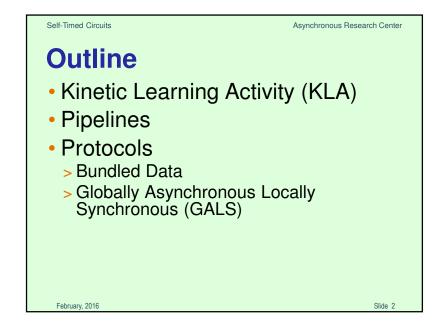

# Understanding Self-Timed Circuits Talk Series Outline

# **Marly Roncken and Ivan Sutherland**

Asynchronous Research Center (ARC) Maseeh College of Engineering and Computer Science Portland State University January-February 2016

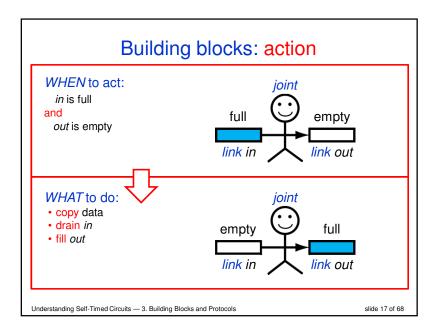

# **Understanding Self-Timed Circuits**

# PART I

TUESDAY afternoon, 16 Feb 2016

- 1. Introduction (Marly)

- 2. Self-Timed Circuits (Ivan)

- 3. Building Blocks and Protocols (Marly)

- 4. Measuring Performance (Ivan)

# PART II

WEDNESDAY morning, 17 Feb 2016

- 5. Timing Validation (Marly)

- 6. Arbitration: Who wins? (Ivan)

- 7. Initialization, Test, and Debug (Marly)

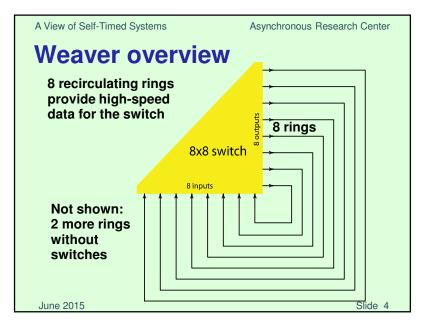

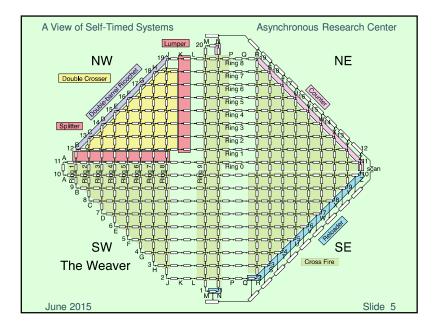

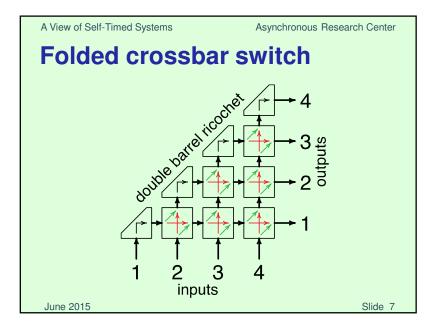

- 8. The Weaver (Ivan)

slide 2 of 2

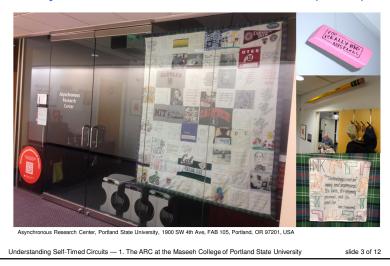

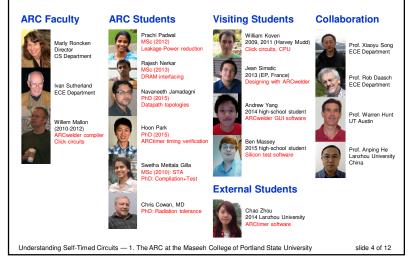

#### Asynchronous Research Center (ARC)

# Asynchronous Research Center (ARC)

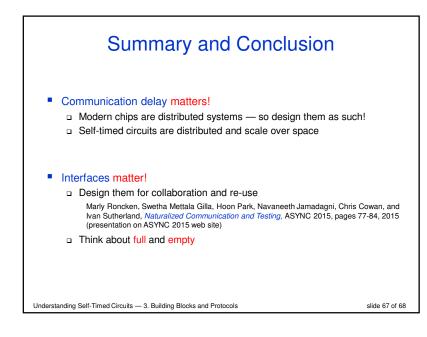

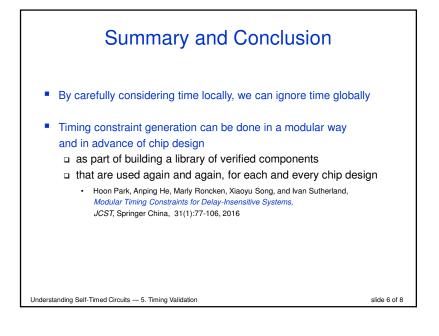

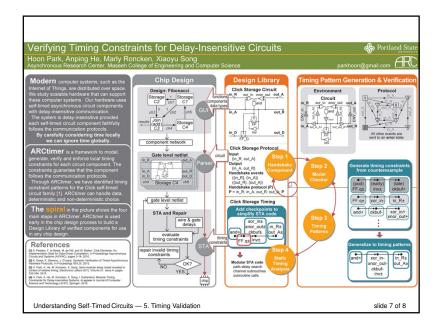

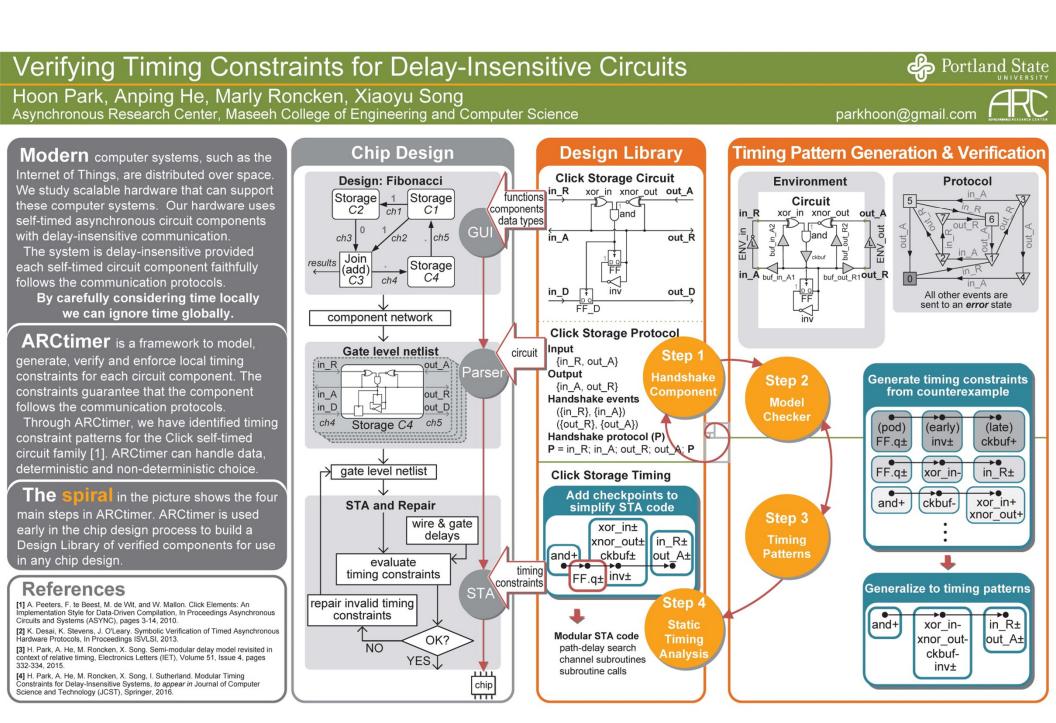

#### A sample about our work Hoon Park, Anping He, Marly Roncken, Xiaoyu Song, Ivan Sutherland Modular Timing Constraints for Delay-Insensitive Systems JCST, Springer China, 31(1):77-106, 2016 Hoon Park, Anping He, Marly Roncken, and Xiaoyu Song Semi-modular delay model revisited in context of relative timing IET Electronics Letters, 51(4):332-334, 2015 Marly Roncken, Swetha Mettala Gilla, Hoon Park, Navaneeth Jamadagni, Chris Cowan, and Ivan Sutherland Naturalized Communication and Testing ASYNC 2015, pages 77-84, 2015 (presentation on ASYNC 2015 web site) Poster by Hoon on Timing Validation (see ASYNC 2015 web site) Poster by Swetha on Testing with MrGO (see ASYNC 2015 web site) Ivan Sutherland GasP Circuits that Work ECE 507 Seminar, Fall 2010, Asynchronous Research Center. http://arc.cecs.pdx.edu/fall10 Understanding Self-Timed Circuits - 1. The ARC at the Maseeh College of Portland State University slide 6 of 12

#### Where on earth are we? (2/2)**Portland**, the largest city in Oregon and seat of Multnomah County, is located in the northwest part of the state on the Willamette River. Portland Over **1**,700 high-tech companies are located in the metropolitan area. Portland is one of the fastest growing tech sectors in the country, and home to major industrial players in Microelectronics · Energy and power Manufacturing · Transportation and other infrastructure technology. the state of OREGON Portland boasts a thriving creative, recreation and culinary culture. Understanding Self-Timed Circuits - 1. The ARC at the Maseeh College of Portland State University slide 8 of 12

#### 2

# Regional industry

# <section-header>Agasech College at a glance94 faculy members with 86 teaching faculy5 departments6 divid and Environmental Engineering6 lectrical and Computer Engineering8 dechaical and Materials Engineering9 dechaical and Materials9 dechaical and Materiala and Materials

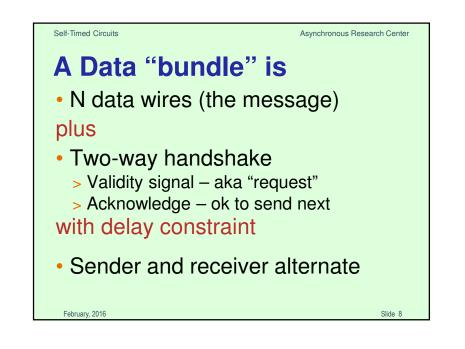

#### Self-Timed Circuits

Asynchronous Research Center

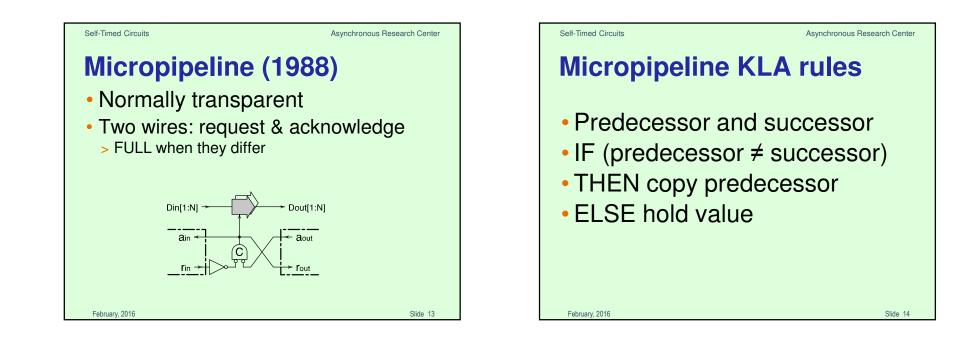

# **KLA rules**

- Predecessor and successor

- Use only one hand

- Pred has object AND you don't

- Do: TAKE from predecessor

- Never: PUT to successor

February, 2016

Slide 3

Slide 10

# Motivation: why asynchronous? [1/9]

- Modern computer systems are distributed over space

- Examples:

#### Internet of things

the network of physical objects or "things" embedded with electronics, software, sensors, and network connectivity, which enables these objects to collect and exchange data [Wikipedia]

#### IBM's TrueNorth

modular chips that act like neurons and form artificial neural networks to run "deep learning algorithms", like Skype's chat translator or Facebook's facial recognition

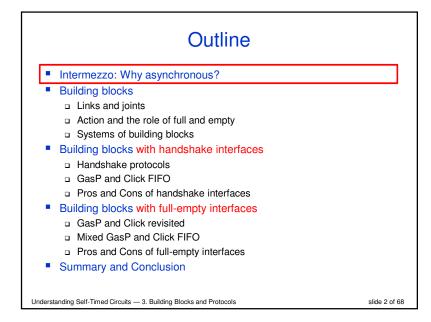

Understanding Self-Timed Circuits - 3. Building Blocks and Protocols

slide 4 of 68

# INTERMEZZO: Why Asynchronous or Self-Timed?

Understanding Self-Timed Circuits - 3. Building Blocks and Protocols

slide 3 of 68

# Motivation: why asynchronous? [2/9]

- We can manage time + communication delay over space, provided

synchronicity is required only over short distances

- long-distance communication relies on causality i.e. event orderings (+ communication delay)

- Examples:

- It took 4 hours to get the final position commands from Earth to New Horizons near Pluto, in order to make this picture of Pluto and its moon Charon. [www.planetary.org/blogs/emlty-lakdawalla/2015/01300800-talking-to-pluto-is-hard.html]

In August 2012, NASA landed *Curiosity* on Mars. At the time, Mars was 13 minutes talk-time away. The landing was on autopilot, the last 13 minutes. [http://mars.nasa.gov/msi]

Curiosity "selfie"

Understanding Self-Timed Circuits - 3. Building Blocks and Protocols

slide 5 of 68

# Motivation: why asynchronous? [3/9]

- Technology can make a space look smaller

so that synchronicity can be maintained over a longer distance

- Examples:

- Rail transport took over transport by horse and introduced traveling "on time"

- Global Positioning System (GPS) [Roger L. Easton, Ivan A. Getting, Bradford Parkinson, 1978]

- Internet (communication network) [Internet protocols: TCP/IP Vint Cerf, Bob Kahn, 1974]

- World Wide Web (information space) [Tim Berners-Lee, 1989]

- Email, Dropbox, Skype, TeamViewer for our Portland-Lanzhou meetings

After building a train station on Germany's railway, the hours on the tower clock in Speyer (top) no longer sufficed. An extra clock (bottom) was added to show the minutes in each hour.

Understanding Self-Timed Circuits - 3. Building Blocks and Protocols

slide 6 of 68

# Motivation: why asynchronous? [4/9]

- Or technology can make a space look BIGGER

making us dive head on into synchronicity limits

- Example:

Nanometer chip technology enables more and faster transistors per chip but the wires scale less well, and are therefore much slower. As a result:

- Global clocks are too slow for modern chips

- It takes hundreds of clock domains, ten thousand signals crossing them, and many clock ticks, to communicate within a single networking chip Jeanne Trinko, IBM, Keynole Speech ASYNC 2013

Modern chips are distributed systems

Understanding Self-Timed Circuits — 3. Building Blocks and Protocols

slide 7 of 68

# Motivation: why asynchronous? [5/9]

- We design and study hardware

- distributed over self-timed components + communication protocols

Understanding Self-Timed Circuits - 3. Building Blocks and Protocols

slide 8 of 68

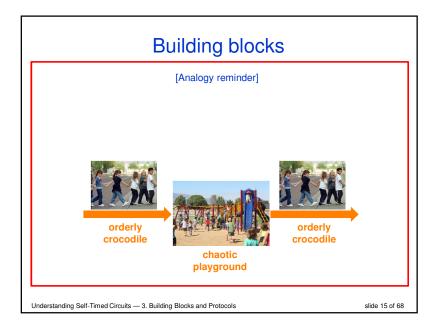

# Motivation: why asynchronous? [6/9]

- Inside a component

- behavior can be as chaotic as a kindergarten playground

- which is fine, because the space is small enough to synchronize events

Understanding Self-Timed Circuits — 3. Building Blocks and Protocols

slide 9 of 68

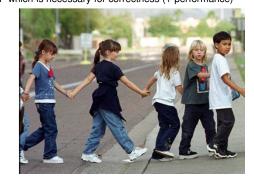

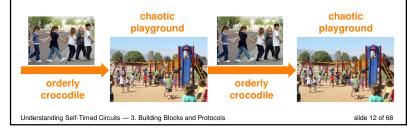

# Motivation: why asynchronous? [7/9]

- The communication protocols between the components

- are based on event orderings (+ communication delay)

and are as orderly as a "crocodile"

- which is necessary for correctness (+ performance)

slide 10 of 68

# Motivation: why asynchronous? [8/9]

#### Summary:

#### We design and study hardware

$\hfill\square$  distributed over self-timed components + communication protocols where

- Inside a component it can be as chaotic as a kindergarten playground which is fine, because components are small enough to control events

- Between components, the protocols are as orderly as a "crocodile" which guarantees that the communication is correct

# Motivation: why asynchronous? [9/9]

- The playground system works, provided local supervisors

oversee the playground to avoid accidents, bullying, fights

ensure children use the "crocodile" between playgrounds

- Hardware analogy:

Understanding Self-Timed Circuits - 3. Building Blocks and Protocols

- accidents: wrong handshake protocol, ignored transitions, drive fights

supervisors: event ordering constraints, a.k.a. relative timing constraints

- This is a scalable system because the supervisors are local

####

# <section-header><section-header><section-header><list-item><list-item><list-item><list-item><list-item><list-item><list-item><table-row><table-container>

# Self-Timed Circuits Asynchronous Research Center **Ring oscillator** • Odd number of stages (3) All same size Any size If different sizes some may fail to reach the rails Slide

February, 2016

#### Self-Timed Circuits

#### Asynchronous Research Center

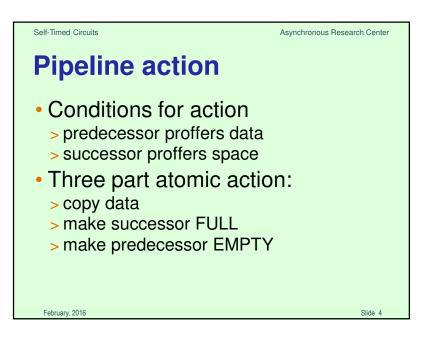

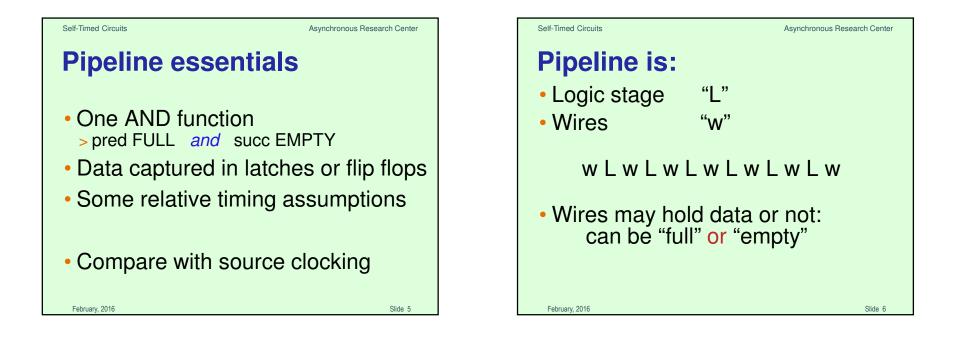

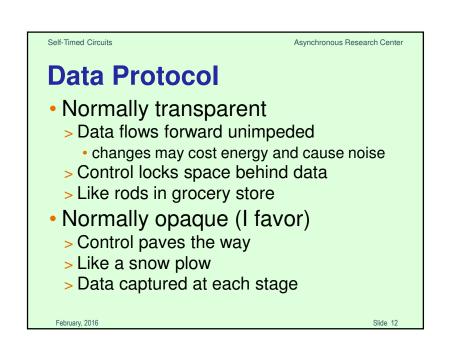

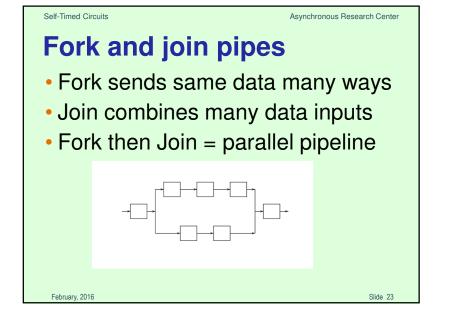

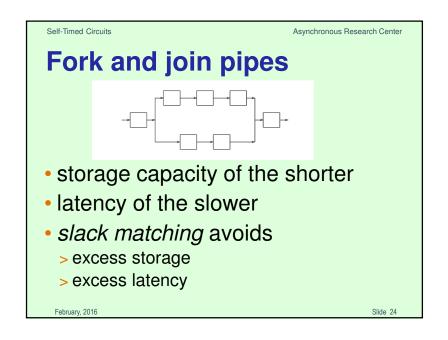

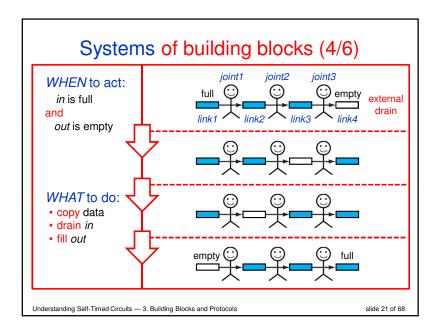

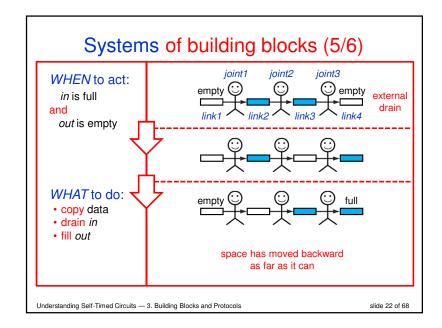

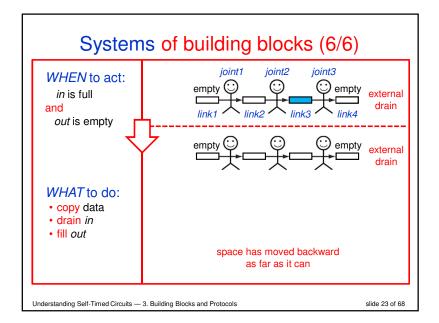

# Self-timed pipelines (cont'd)

- Data Items move toward output

- >Remaining in sequence

- > Data items can't overtake others

- Spaces move toward input

- > By exchange with data items

- Analogies:

- >one lane road

- >queue of people at bus stop

#### February, 2016

Asynchronous Research Center

# *NOT* a ring buffer FIFO

- A section of RAM can be a FIFO

- Read and write pointers

- Pointer arithmetic computes FULL

- Each cycle *either* reads or writes

- Contrast with self-timed FIFO reading and writing concurrently.

#### Self-Timed Circuits

February, 2016

Self-Timed Circuits

#### Asynchronous Research Center

Slide 10

Asynchronous Research Center

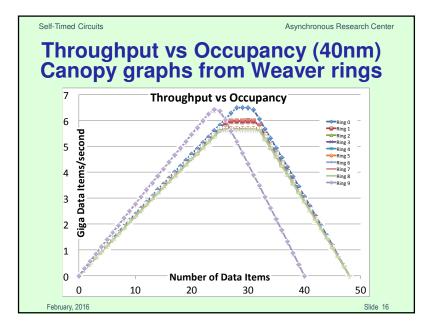

# Self-timed pipelines (cont'd)

- How fast do data move?

- > Depends on the circuit

- How fast do spaces move?

Depends on the circuit

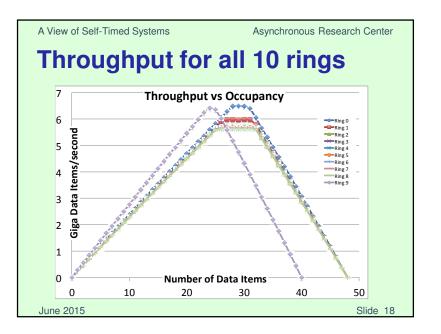

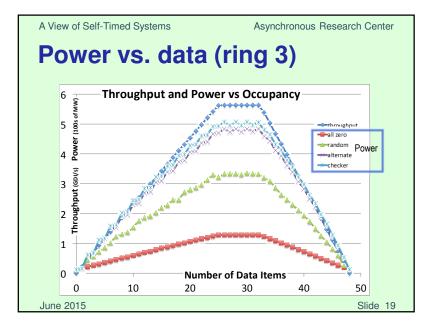

- "Canopy Graph" shows speed

- Introduced by Ted Williams (PhD 1991)

- Named by Gill and Singh (Gill's PhD 2010)

#### Self-Timed Circuits

February, 2016

Asynchronous Research Center

Slide 9

Slide 11

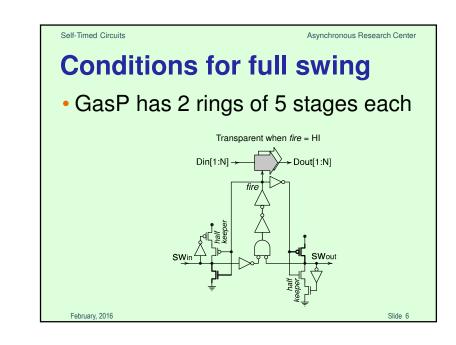

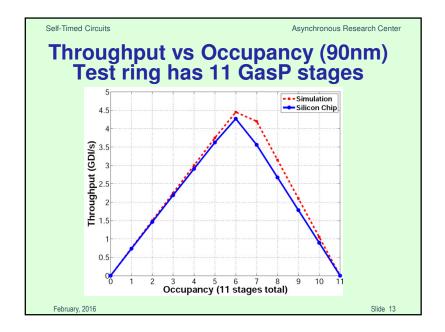

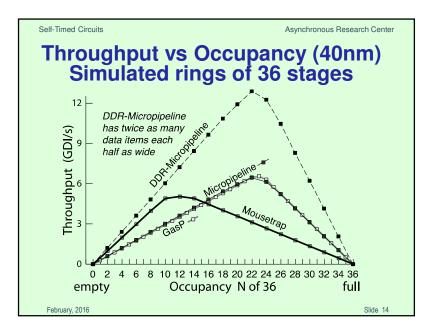

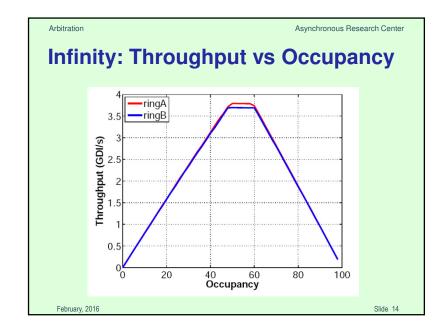

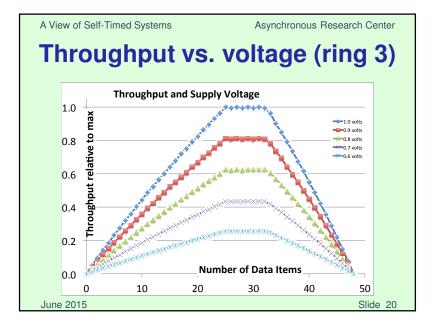

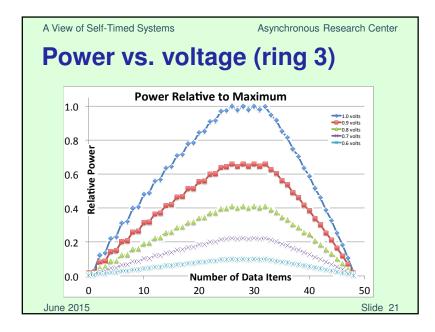

# **Canopy graphs**

- Throughput versus occupancy

throughput in items/time: GDI/s

- > occupancy in items/stage from 0 to 1

- > occupancy in items/stage from 0 to 1

- No occupancy = no throughput

- Full occupancy = no throughput

- Occupancy for max throughput

- Calculated for a ring

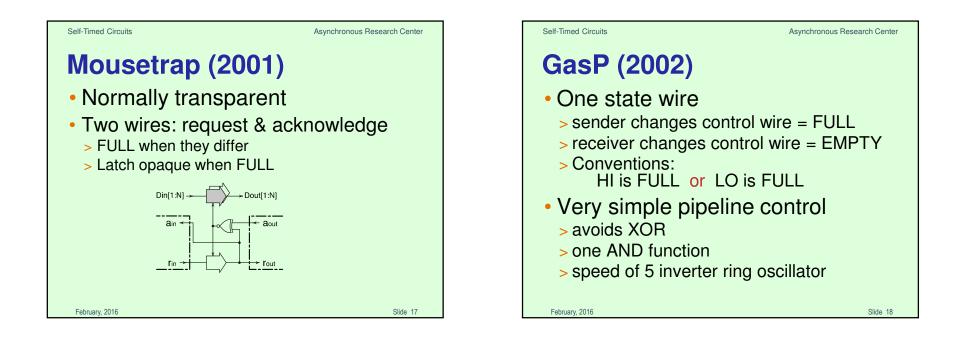

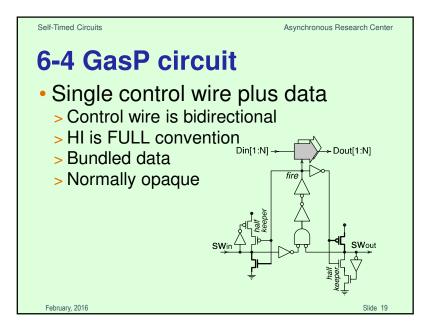

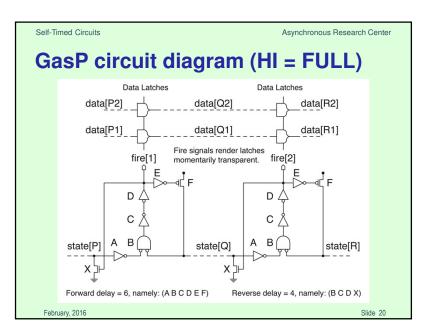

GasP circuit diagram (HI = FULL)

| Self-Timed Circuits |         | Asynchronous Research Center |

|---------------------|---------|------------------------------|

|                     | Discuss |                              |

| February, 201       | 3       | Slide 19                     |

Self-Timed Circuits

February, 2016

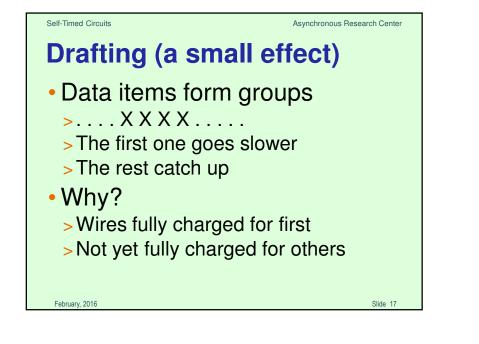

### Drafting (cont'd)

- We know by many stops

- > Where were the tokens at stop?

- > How many got past (statistically)?

- Measured only in rings

After passing billions of stages

- Now doing experiments to observe onset of drafting

Slide 18

Asynchronous Research Center

### Asynchronous design: reminder (1/4)

### • We design and study hardware

□ distributed over self-timed components + communication protocols

### where

- Inside a component it can be as chaotic as a kindergarten playground which is fine, because components are small enough to control events

- Between components, the protocols are as orderly as a "crocodile" which guarantees that the communication is correct

### Asynchronous design: reminder (2/4)

### The playground system works, provided local supervisors

oversee the playground to avoid accidents

ensure children use the "crocodile" between playgrounds

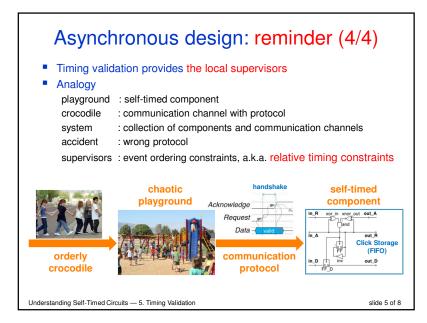

# Asynchronous design: reminder (3/4) Timing validation provides the local supervisors Analogy playground : self-timed component crocodile : channel connection with communication protocol system : collection of components and communication channels accident : wrong protocol supervisors : event ordering constraints, a.k.a. relative timing constraints

### Understanding Self-Timed Circuits — 5. Timing Validation

# <section-header> Outline Quantize a continuous variable Time is the variable What happened first Exactly the same time? Arbiter circuit Decides, but may take time

Asynchronous Research Center

Arbitration

Asynchronous Research Center

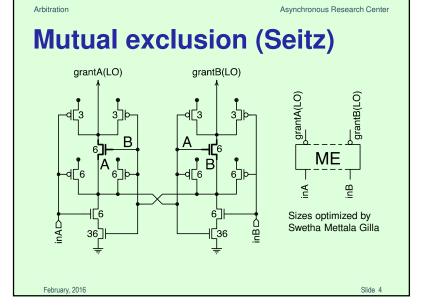

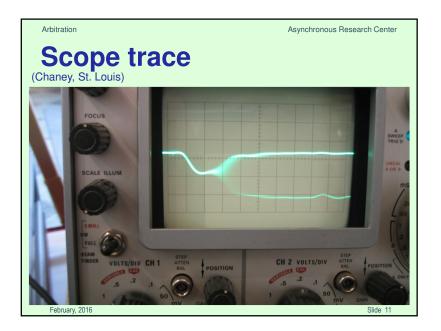

## **Mutual exclusion**

- Two events at "same" time

- > which choice doesn't matter

- >but choice must be clean

- Flip-flop can hang metastable

> exit is Poisson distributed

- > may take a long time, but rarely will

- Asynchronous system can wait

February, 2016

Arbitration

Slide 3

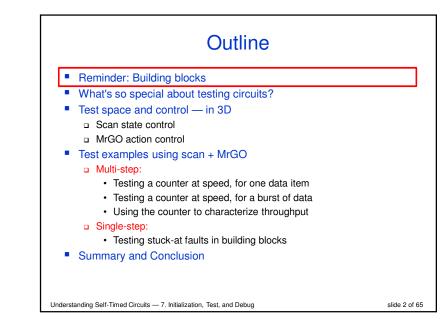

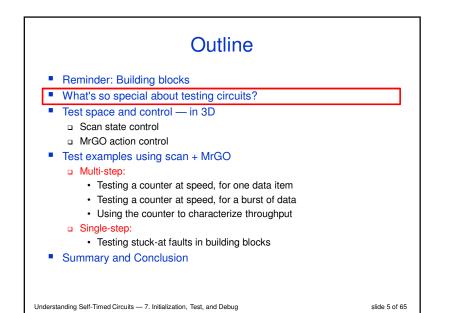

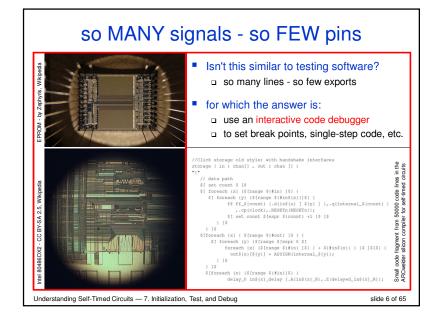

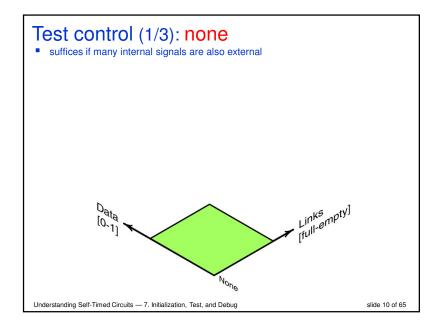

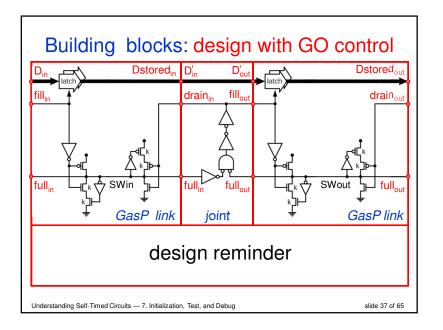

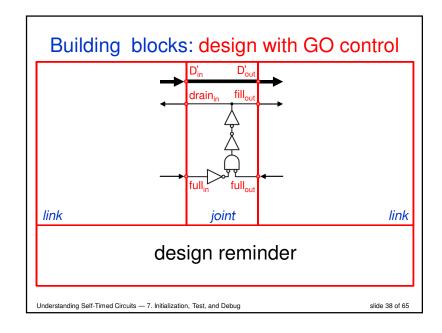

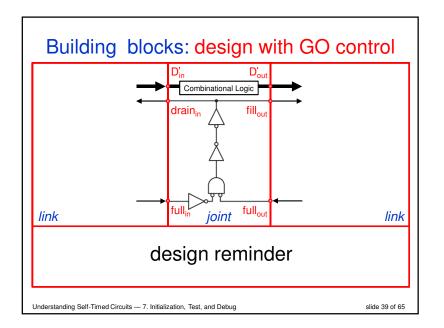

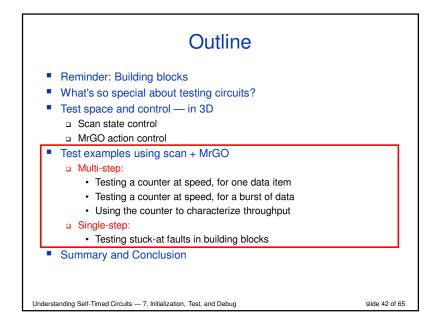

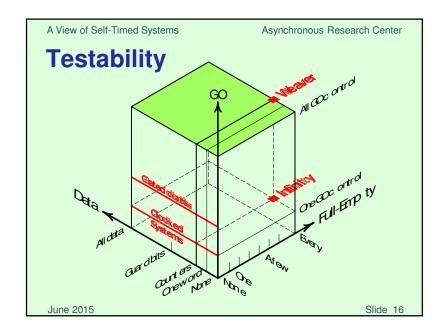

| Outline                                                                      |  |

|------------------------------------------------------------------------------|--|

| Reminder: Building blocks                                                    |  |

| What's so special about testing circuits?                                    |  |

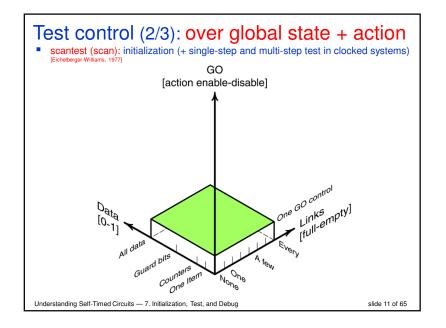

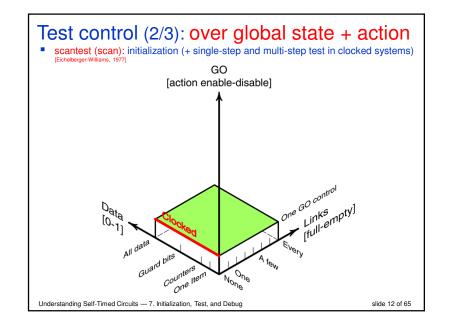

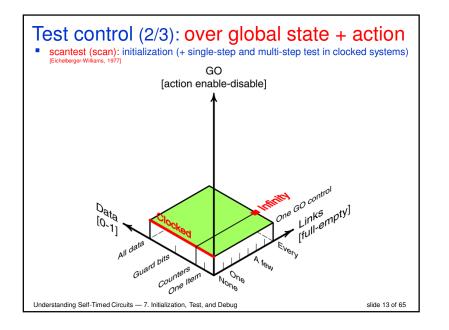

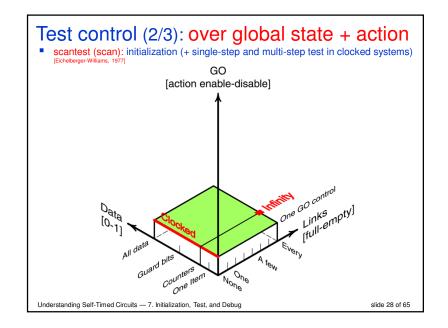

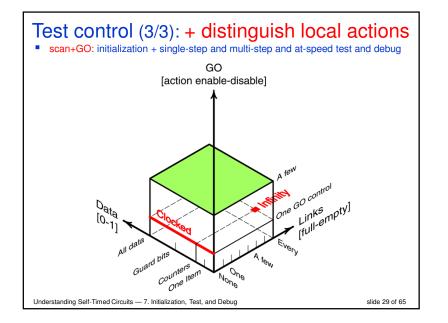

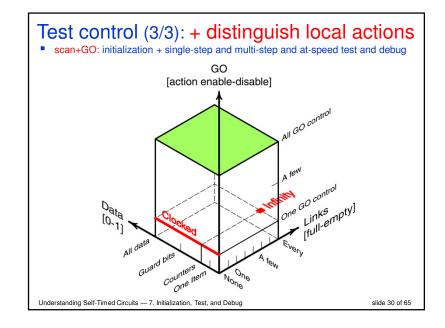

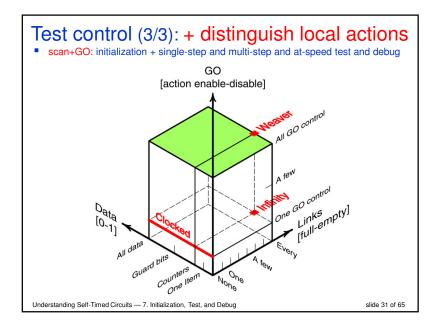

| Test space and control — in 3D                                               |  |

| Scan state control                                                           |  |

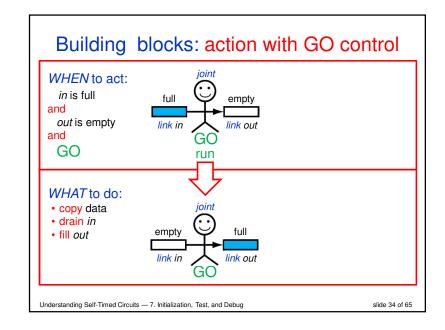

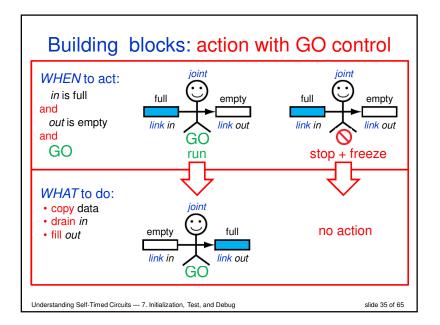

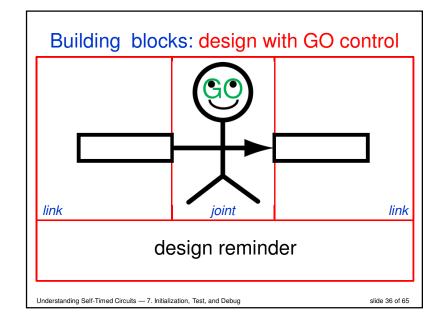

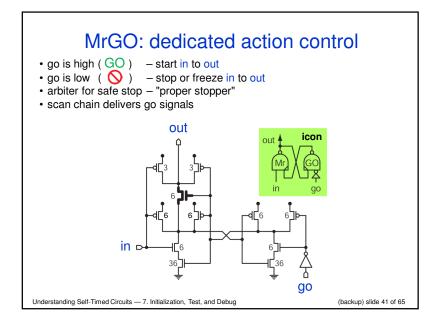

| MrGO action control                                                          |  |

| Test examples using scan + MrGO                                              |  |

| Multi-step:                                                                  |  |

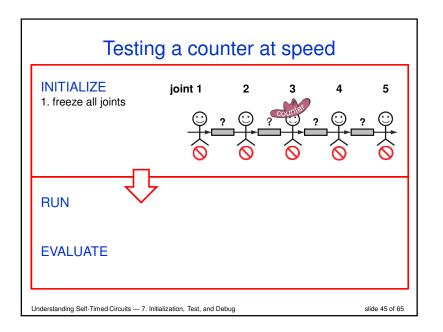

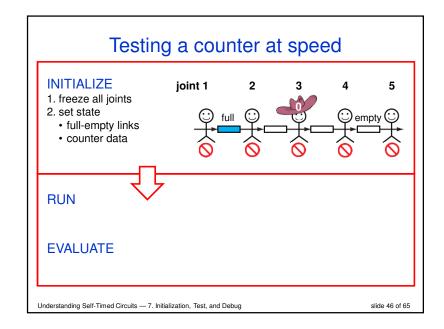

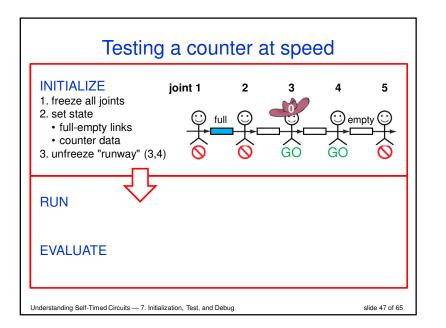

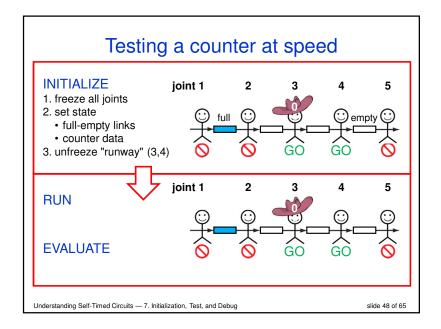

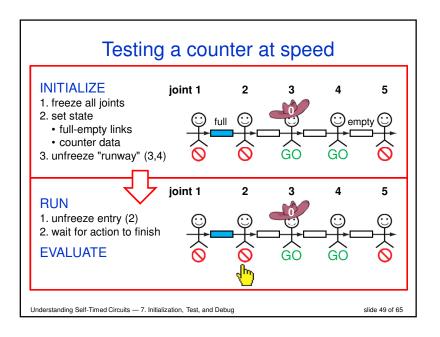

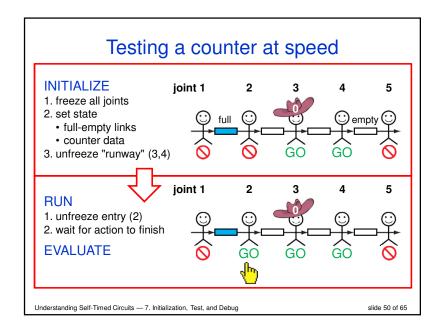

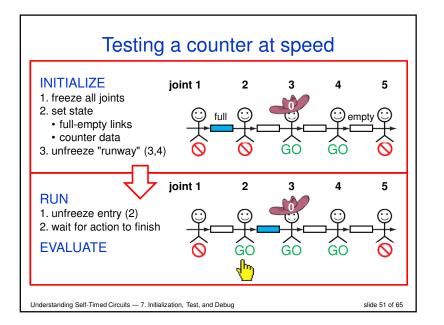

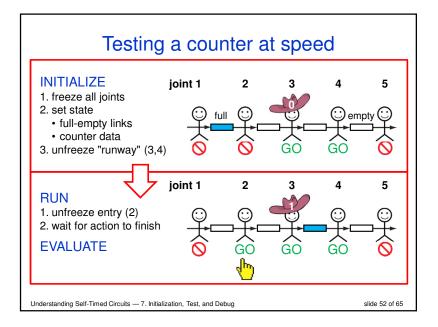

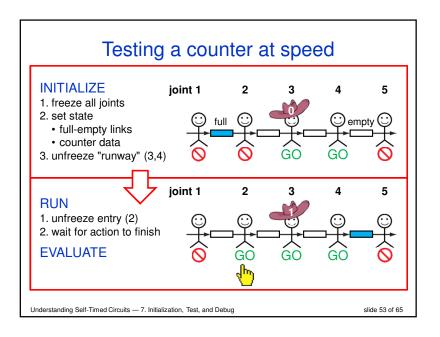

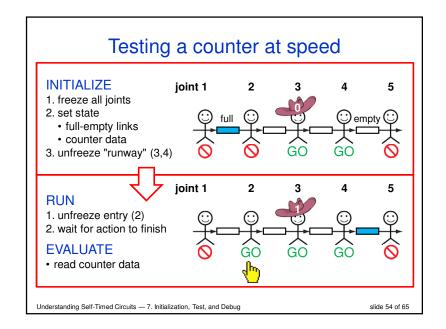

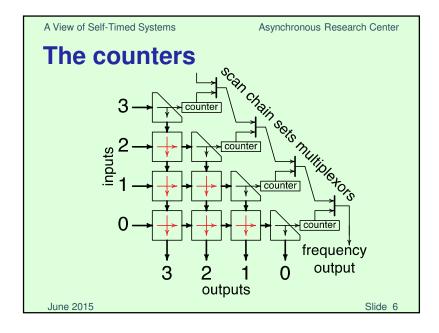

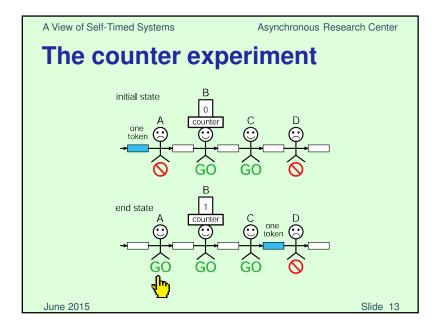

| <ul> <li>Testing a counter at speed, for one data item</li> </ul>            |  |

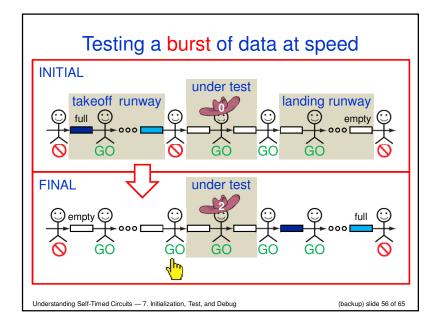

| <ul> <li>Testing a counter at speed, for a burst of data</li> </ul>          |  |

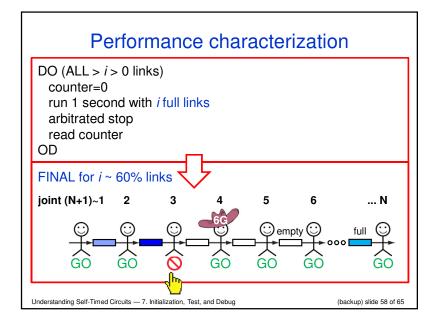

| <ul> <li>Using the counter to characterize throughput</li> </ul>             |  |

| <ul> <li>Single-step:</li> </ul>                                             |  |

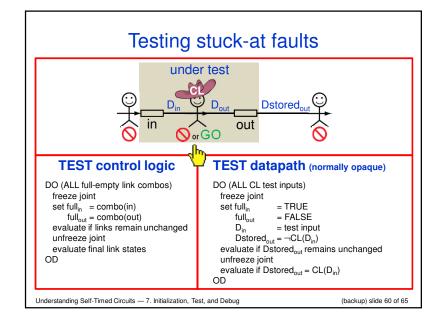

| <ul> <li>Testing stuck-at faults in building blocks</li> </ul>               |  |

| Summary and Conclusion                                                       |  |

|                                                                              |  |

| Understanding Self-Timed Circuits — 7. Initialization, Test, and Debug slide |  |

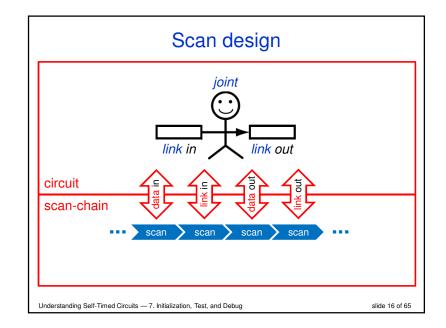

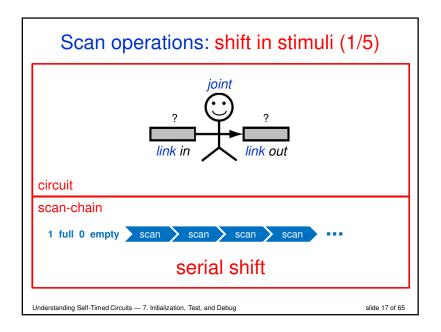

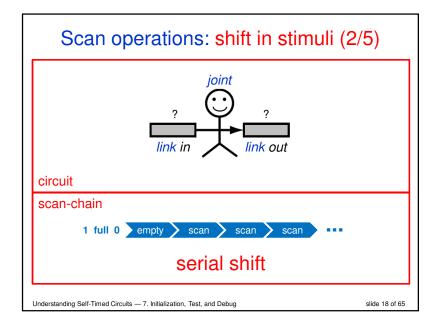

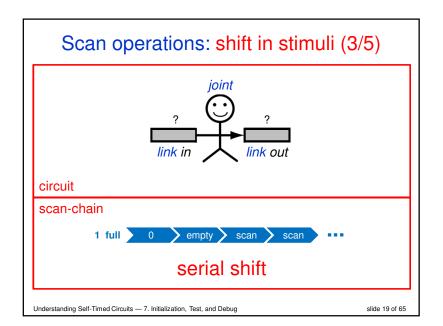

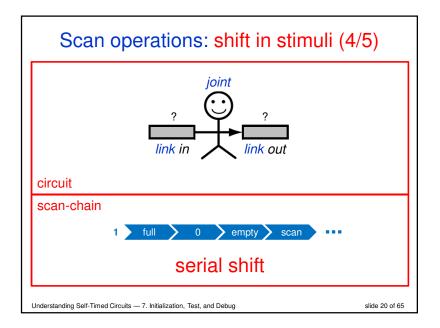

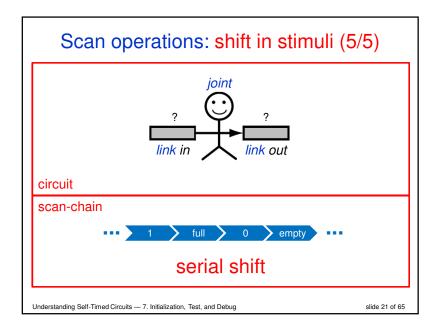

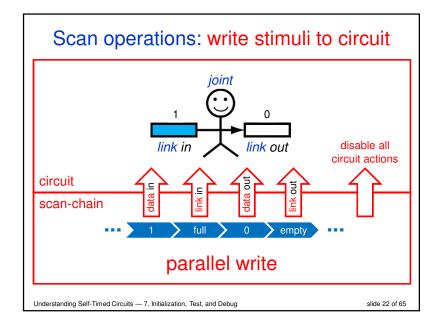

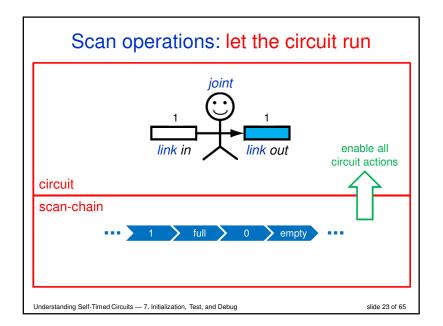

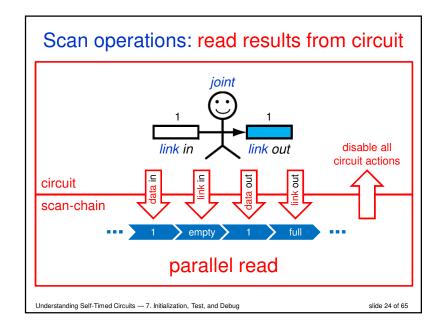

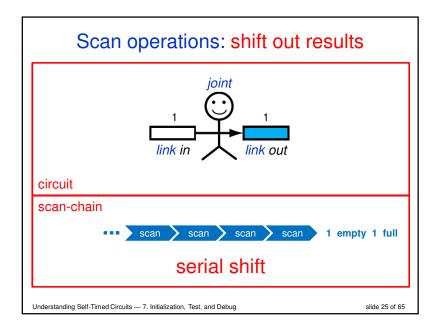

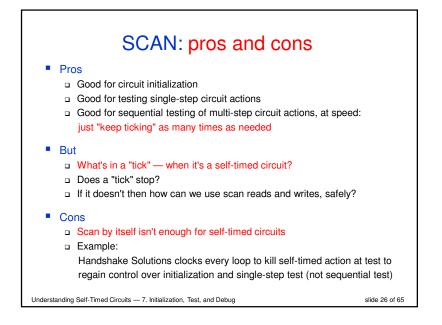

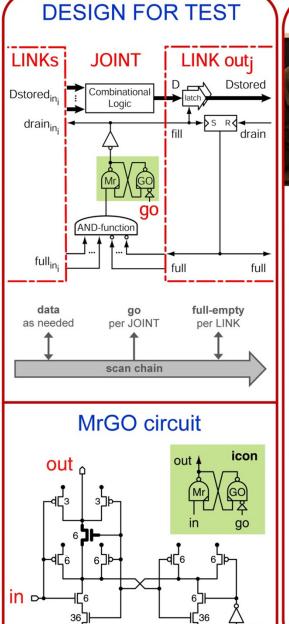

### Scan design Scan-chain Can store + move (shift) data Entry and exit are external • Can write data from the scan chain into internal circuit signals • Can read internal circuit signals and store their values in the scan chain Scan-control □ For scan operations: shift, write, read, enable-disable circuit action □ Can be self-timed or clocked; we use clocked, because • it doesn't matter: systems operate independent of how they're tested · IEEE standards are available circuit scan-chain scan scan scan scan ....

slide 15 of 65

Understanding Self-Timed Circuits - 7. Initialization, Test, and Debug

## **Testing Self-Timed Circuits with MrGO**

Swetha Mettala Gilla, Marly Roncken, Ivan Sutherland, Xiaoyu Song Asynchronous Research Center, Portland State University (mettalag@cecs.pdx.edu)

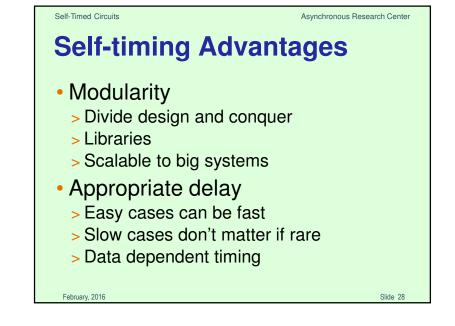

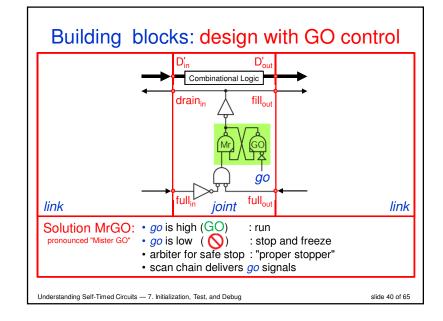

### MOTIVATION

### Why self-timed?

- · Self-timed circuits offer modularity

- · Self-timed circuits offer energy efficiency

- · Self-timed circuits offer speed

### What?

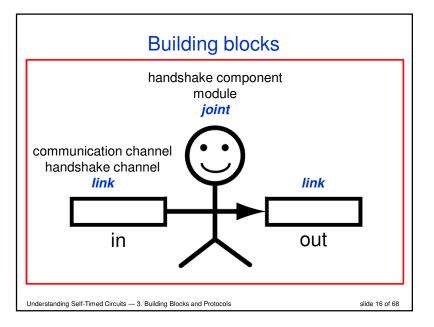

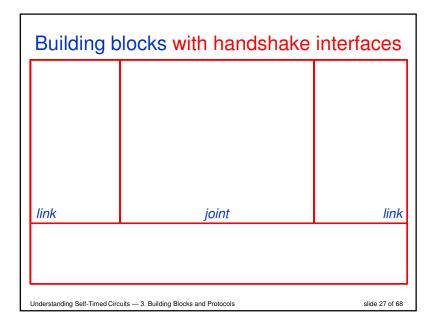

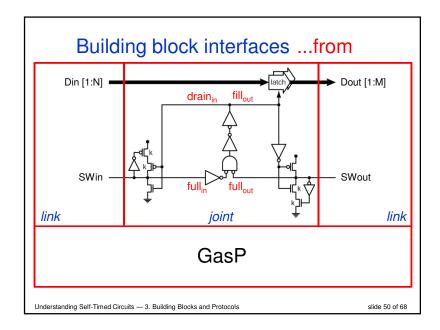

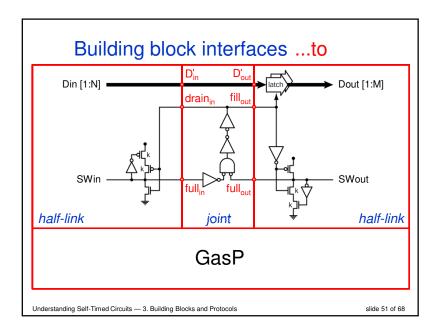

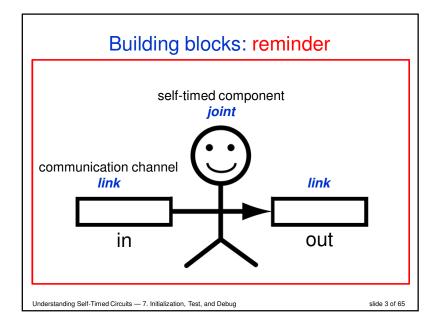

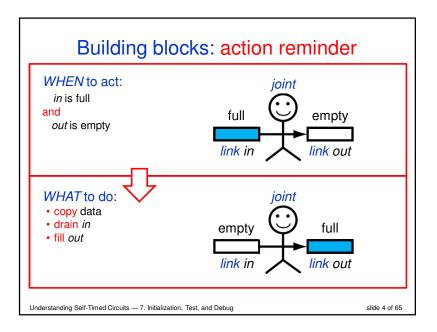

- Self-timed networks of state-holding *links* (□)

- Exchange data at action-capable joints

### Wanted:

- A general test method to initialize states and control actions for:

- 1. structural fault testing,

- 2. at-speed testing, and

- 3. debug

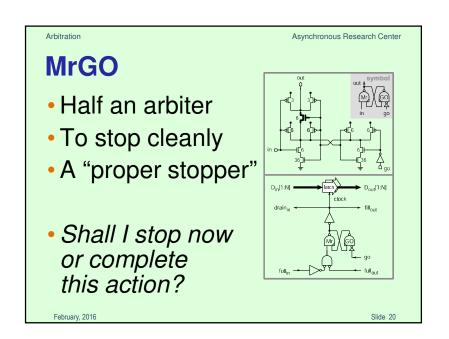

### SOLUTION

- *(Well-known)* scan chain to initialize and observe link states

- (New) MrGO

- to control individual joint actions

- go is high (GO) run

- go is low (🚫) stop

- arbiter for safe stop "proper stopper"

- · scan chain delivers go signals

### REFERENCES

- [1] M. Bushnell and V. Agrawal, "Essentials of Electronic Testing for Digital, Memory, and Mixed-Signal VLSI Circuits," Springer, 2005.

- [2] C. Molnar, I. Jones, W. Coates, and J. Lexau, "A FIFO Ring Performance Experiment," ASYNC, pp. 279–289, 1997.

- [3] M. Roncken, "Defect-Oriented Testability for Asynchronous ICs," Proceedings of the IEEE, Vol. 87, No. 2, pp. 363–375, Feb. 1999.

- [4] M. Roncken, S. Mettala Gilla, H. Park, N. Jamadagni, C. Cowan, I. Sutherland, "Naturalized Communication and Testing," ASYNC 2015.

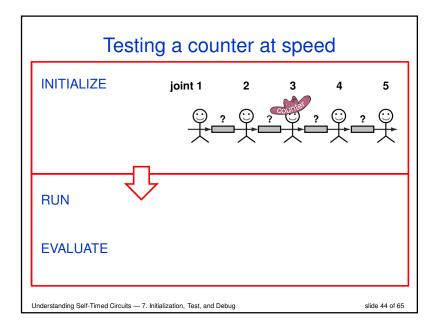

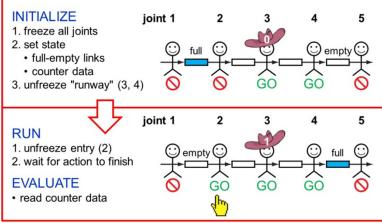

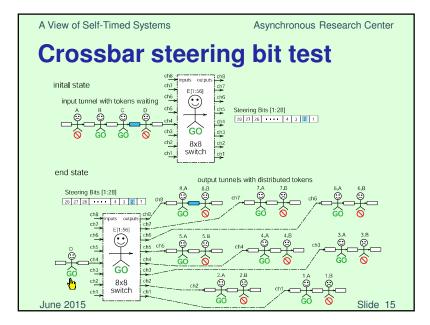

### TEST EXECUTION

### Example: testing a counter at speed

### Supports:

qo

- 1. Initialization

- 2. Arbitrated stop from full speed

- 3. Single- and multi-step operations

- 4. At-speed testing of sub-systems

- 5. Canopy graph generation

- 6. Testing of structural faults like stuck-at

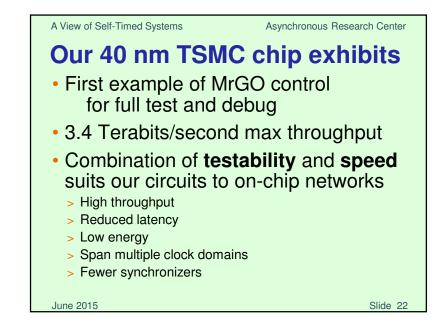

Is built into the latest ARC-Oracle test chip AND IT WORKS !

# Algebrack States Algebrack States Algebrack States Algebrack States Algebrack States Algebrack State Algebra

# UNDERSTANDING **SELF-TIMED CIRCUITS**

Professor Ivan Sutherland Professor Marly Roncker 时间: 2016年2月25日上午9点 地点:复旦大学张江校区行政楼第

all modern digital computers march to the beat of a The computer clock divides each second into a "lion "clock periods" just as a school bell divides each to fixed-length class periods. A 55-minute class so useful for scheduling students and classrooms tors rarely ask if it is best for learning. In reality, is either too short or too long.

of a few research groups who study how to rigid clock with more flexible "self-timed" If-timed systems allow each small task to take dural time just as "self-paced" learning allows int to learn at his or her own natural pace. Easy quickly and take little energy. Difficult tasks e time and energy.

nion a self-timed system is as orderly as a kinderlayground at recess. Marly and Ivan will show how of such a system interact, and how they can be gned, validated, and tested.

y Roncken and Ivan Sutherland have each worked self-timed systems for more than 25 years. They ed forces by marriage in 2006. Marly, a mathematician raining, focuses on logic, structure, and correctness. n, an electrical engineer by training, designs circuits systems. Together they run the Asynchronous sarch Center (ARC) at Portland State University U). Ivan is best known for his early work in computer ics, a field he left in 1976. Since his Turing Award te in 1988 he has dedicated his work to escaping from

# Fudan University, Shanghai