#### Silicon Compilation and Test for Dataflow Implementations in GasP and Click

by

#### Swetha Mettala Gilla

A dissertation submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy in Electrical and Computer Engineering

Dissertation Committee:

Xiaoyu Song, Chair

Douglas V. Hall

Robert W. Daasch

Ivan E. Sutherland

Mark P. Jones

Marly Roncken (non-voting member)

Portland State University 2018

#### **ABSTRACT**

Many modern computer systems are distributed over space. Well-known examples are the Internet of Things and IBM's TrueNorth for deep learning applications. At the Asynchronous Research Center (ARC) at Portland State University we build distributed hardware systems using self-timed computation and delay-insensitive communication. Where appropriate, self-timed hardware operations can reduce average and peak power, energy, latency, and electro-magnetic interference. Alternatively, self-timed operations can increase throughput, tolerance to delay variations, scalability, and manufacturability.

The design of complex hardware systems requires design automation and support for test, debug, and product characterization.

My PhD thesis focuses on design compilation and test support for dataflow applications. Both parts are necessary to go from self-timed circuits to large-scale hardware systems.

As part of my research in design compilation, I have extended the ARCwelder compiler designed by Willem Mallon (previously with NXP and Philips Handshake Solutions). The resulting ARCwelder compiler can support multiple self-timed circuit families.

The key to testing distributed systems, including self-timed systems, is to identify the actions in the systems. In distributed systems there is no such thing as a global action. To test, debug, characterize, and even initialize distributed systems, it is necessary to control the local actions - individually! The designs that we develop at the ARC separate the actions from the states *ab initio*.

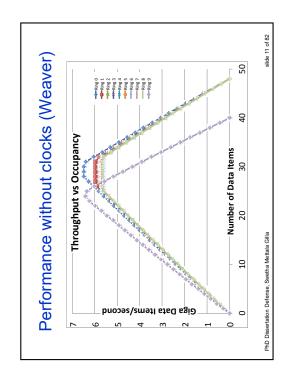

As part of my research in test and debug, I implemented a special circuit to control actions, called MrGO. I also implemented a scan and JTAG test interface to take control over each individual and local action, each individual and local communication state, and any subset of data-related state elements one might wish to control or observe. My test implementations have been built into two silicon test experiments, called Weaver and Anvil, and were used successfully for testing, debug, and performance characterizations.

## **Acknowledgments**

Firstly, I want to thank my advisor, Drs. Marly Roncken, for her guidance during my research and study at Portland State University (PSU). She is not only my advisor, she is also a mentor and my role model. Her push and consistent motivation helped cross hurdles and gave me the courage and patience to finish my thesis.

I was delighted to interact with Dr. Ivan Sutherland. It was a great opportunity to work with him on arbiter circuits. His insight in asynchronous circuit design is amazing. He explains anything that looks like "eschew obfuscation" into something as obvious as "keep it simple" <sup>1</sup>. To me, he defines what a world-class researcher and teacher are about.

I am much obliged to Professor Xiaoyu Song, for agreeing to be my thesis advisor. One simply could not wish for a more friendly and understanding advisor. Professor Douglas V. Hall, Professor Robert Daasch and Professor Mark Jones deserve special thanks as my dissertation committee members. I sincerely appreciate their participation and technical feedback. I thank Willem Mallon for sharing his knowledge on compilers. Willem is the greatest programmer I have ever met, as well as a selfless and kind human being.

Special thanks go to my colleagues Chris Cowan, Navaneeth Jamadagni, Hoon Park and Chris Chen for the many technical and non-technical discussions and for making this research fun.

<sup>&</sup>lt;sup>1</sup>The text "eschew obfuscation" is on one of his sweatshirts.

I am indebted to my parents and my in-laws for their care and love. I thank you for believing in me and for supporting my study and career decisions.

I owe thanks to a very special person, my husband Ravi, for his continued love and support. He deserves the same amount of credit as I do for this work. I thank my baby, my little girl Swara, for abiding my absence. My heartfelt thanks go to my mother-in-law for taking my place in mothering Swara during the last phase of my PhD research.

TABLE OF CONTENTS vi

# **Table of Contents**

| Ak  | strac   | t                                          | i   |

|-----|---------|--------------------------------------------|-----|

| De  | edicat  | ion                                        | iii |

| Ac  | know    | rledgments                                 | iv  |

| Lis | st of T | Tables Tables                              | хi  |

| Lis | st of F | Figures                                    | xii |

| 1   | Intro   | oduction                                   | 1   |

|     | 1.1.    | Research Objective and Approach            | 2   |

|     | 1.2.    | Research Summary                           | 3   |

|     | 1.3.    | My Contributions                           | 6   |

|     | 1.4.    | Thesis Organization                        | 6   |

| 2   | Tele    | scope GasP (TGasP)                         | 9   |

|     | 2.1.    | Why Telescope GasP?                        | 10  |

|     | 2.2.    | Traditional versus Telescope GasP          | 13  |

|     | 2.3.    | Cost of and Alternatives to Telescope GasP | 16  |

|     | 2.4.    | Designing Telescope GasP Modules           | 18  |

|     | 2.5.    | Latency Reduction in the Reverse Direction | 24  |

|     | 2.6.    | Summary and Conclusions                    | 26  |

| TABLE OF CONTENTS | vii |

|-------------------|-----|

| IADLL OF CONTLINE | VII |

|   | 2.7.  | My Contributions for Chapter 2                   | 28 |

|---|-------|--------------------------------------------------|----|

| 3 | Silic | con Compilation for Click and GasP               | 29 |

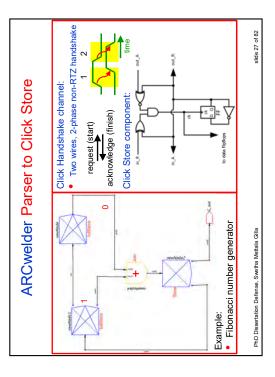

|   | 3.1.  | Existing ARCwelder Compiler                      | 31 |

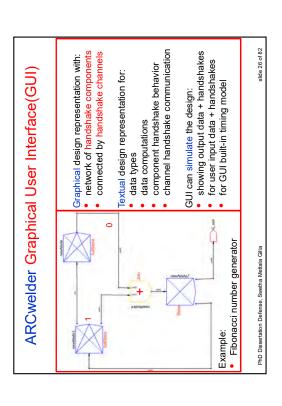

|   |       | 3.1.1. Graphical User Interface                  | 33 |

|   |       | 3.1.2. Parser                                    | 33 |

|   |       | 3.1.3. Static Validation                         | 33 |

|   |       | 3.1.4. Dynamic Validation                        | 33 |

|   | 3.2.  | ARCwelder Compiled Circuits: Existing versus New | 34 |

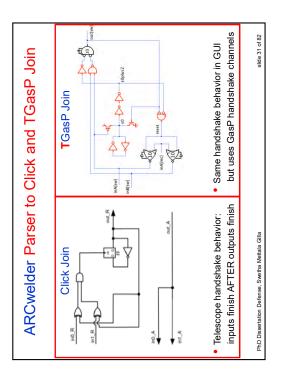

|   | 3.3.  | ARCwelder for Click and (T)GasP                  | 39 |

|   |       | 3.3.1. Graphical User Interface Changes          | 39 |

|   |       | 3.3.2. Parser Changes                            | 41 |

|   |       | 3.3.3. Static Validation Changes                 | 42 |

|   |       | 3.3.4. Dynamic Validation Changes                | 46 |

|   | 3.4.  | ARCwelder Click versus (T)GasP Experiments       | 48 |

|   | 3.5.  | Summary and Conclusion                           | 53 |

|   | 3.6.  | My Contributions for Chapter 3                   | 54 |

| 4 | Natu  | uralized Communication                           | 55 |

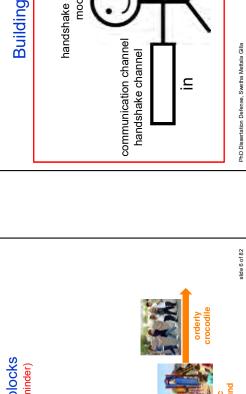

|   | 4.1.  | Systems with Handshake Interfaces                | 57 |

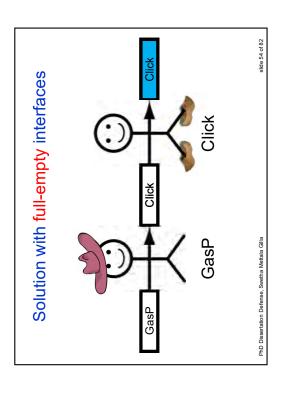

|   | 4.2.  | Systems with Full-Empty Interfaces               | 63 |

|   |       | 4.2.1. Naturalized Links and Joints              | 67 |

|   | 4.3.  | Impact of Naturalization on System Design        | 69 |

|   | 4.4.  | Summary and Conclusion                           | 70 |

|   | 4.5.  | My Contributions for Chapter 4                   | 71 |

| 5 | Natu  | uralized Testing                                 | 73 |

|   | 5.1.  | Testing: Where we Came from, Are, and Go         | 73 |

|   | 5.2.  | Naturalized Testing                              | 77 |

TABLE OF CONTENTS viii

|   |                    | 5.2.1.                                                                                                      | Takeoff: From Initialization to Self-Timed Operation                                                                                                                                                                                                                             | 7                                          |

|---|--------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

|   |                    | 5.2.2.                                                                                                      | Landing: Stopping a Self-Timed Operation in Full Flight 7                                                                                                                                                                                                                        | '8                                         |

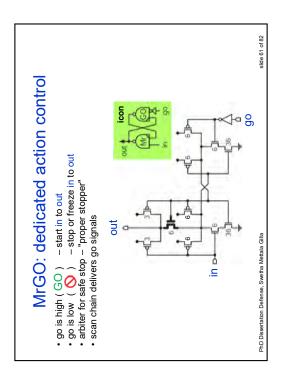

|   |                    | 5.2.3.                                                                                                      | MrGO                                                                                                                                                                                                                                                                             | '9                                         |

|   | 5.3.               | Testing                                                                                                     | with MrGO                                                                                                                                                                                                                                                                        | 0                                          |

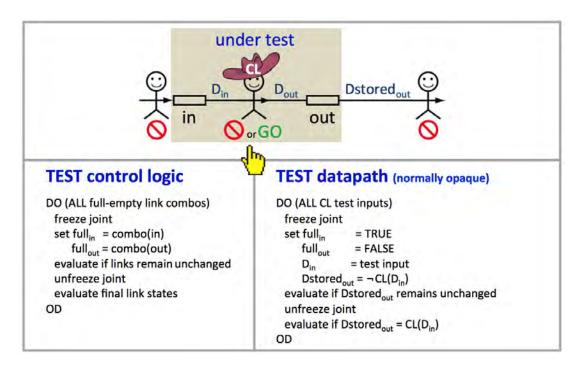

|   |                    | 5.3.1.                                                                                                      | One-shot Test of a Selected Joint                                                                                                                                                                                                                                                | 0                                          |

|   |                    | 5.3.2.                                                                                                      | Following a Thread of Actions                                                                                                                                                                                                                                                    | 1                                          |

|   |                    | 5.3.3.                                                                                                      | Breakpoints                                                                                                                                                                                                                                                                      | ;1                                         |

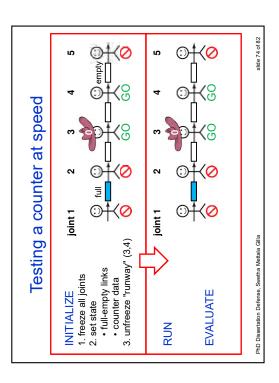

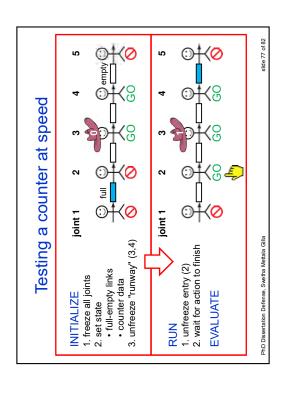

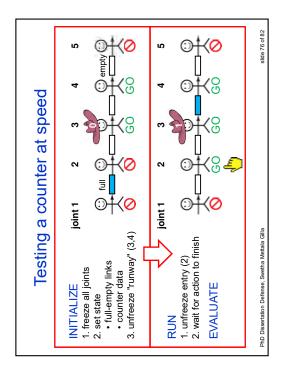

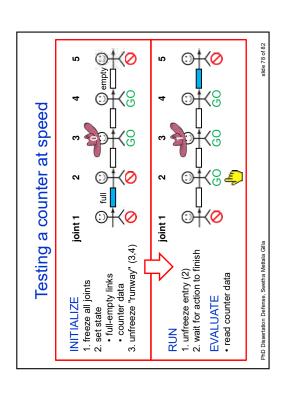

|   |                    | 5.3.4.                                                                                                      | Testing a Single Data Item at Speed                                                                                                                                                                                                                                              | 4                                          |

|   |                    | 5.3.5.                                                                                                      | Testing a Burst of Data Items at Speed                                                                                                                                                                                                                                           | 4                                          |

|   |                    | 5.3.6.                                                                                                      | Testing the Reverse Flow of "Bubbles" at Speed                                                                                                                                                                                                                                   | 4                                          |

|   |                    | 5.3.7.                                                                                                      | Stuck-at Fault Coverage                                                                                                                                                                                                                                                          | 7                                          |

|   | 5.4.               | Summa                                                                                                       | ary and Conclusion                                                                                                                                                                                                                                                               | 8                                          |

|   | 5.5.               | Му Со                                                                                                       | ntributions for Chapter 5                                                                                                                                                                                                                                                        | 8                                          |

|   |                    |                                                                                                             |                                                                                                                                                                                                                                                                                  |                                            |

| 6 | Hier               | archica                                                                                                     | Design for Test and Debug 9                                                                                                                                                                                                                                                      | 1                                          |

| 6 | <b>Hier</b> : 6.1. |                                                                                                             | Design for Test and Debug  e level Test and Debug                                                                                                                                                                                                                                |                                            |

| 6 |                    |                                                                                                             | 3                                                                                                                                                                                                                                                                                | )4                                         |

| 6 |                    | Module                                                                                                      | e level Test and Debug                                                                                                                                                                                                                                                           | )4<br>)7                                   |

| 6 |                    | Module<br>6.1.1.                                                                                            | e level Test and Debug                                                                                                                                                                                                                                                           | )4<br>)7<br>)8                             |

| 6 |                    | Module<br>6.1.1.<br>6.1.2.                                                                                  | Proper Start Control: Make <i>go</i> High                                                                                                                                                                                                                                        | )4<br>)7<br>)8                             |

| 6 |                    | Module<br>6.1.1.<br>6.1.2.<br>6.1.3.<br>6.1.4.                                                              | Proper Start Control: Make <i>go</i> High                                                                                                                                                                                                                                        | )4<br>)7<br>)8<br>)0                       |

| 6 | 6.1.               | Module<br>6.1.1.<br>6.1.2.<br>6.1.3.<br>6.1.4.<br>Design                                                    | Proper Start Control: Make <i>go</i> High 9  Proper Stop Control: Make <i>go</i> Low 9  Full-empty State Control and Observation 10  Data Control and Observation 10                                                                                                             | )4<br>)7<br>)8<br>)0<br>)1                 |

| 6 | 6.1.               | Module<br>6.1.1.<br>6.1.2.<br>6.1.3.<br>6.1.4.<br>Design                                                    | Proper Start Control: Make go High 9 Proper Stop Control: Make go Low 9 Full-empty State Control and Observation 10 Data Control and Observation 10 Level Test and debug 10                                                                                                      | )4<br>)7<br>)8<br>)0<br>)1                 |

| 6 | 6.1.               | Module<br>6.1.1.<br>6.1.2.<br>6.1.3.<br>6.1.4.<br>Design<br>6.2.1.                                          | Proper Start Control: Make go High 9 Proper Stop Control: Make go Low 9 Full-empty State Control and Observation 10 Data Control and Observation 10 Level Test and debug 10 Scan Shift 10                                                                                        | )4<br>)7<br>)8<br>)0<br>)1<br>)7<br>0      |

| 6 | 6.1.               | Module<br>6.1.1.<br>6.1.2.<br>6.1.3.<br>6.1.4.<br>Design<br>6.2.1.<br>6.2.2.                                | Proper Start Control: Make go High 9 Proper Stop Control: Make go Low 9 Full-empty State Control and Observation 10 Data Control and Observation 10 Level Test and debug 10 Scan Shift 10 Non-Destructive Read of Circuit Signals 11                                             | )4<br>)7<br>)8<br>)0<br>)1<br>)7<br>0      |

| 6 | 6.1.               | Module<br>6.1.1.<br>6.1.2.<br>6.1.3.<br>6.1.4.<br>Design<br>6.2.1.<br>6.2.2.<br>6.2.3.<br>6.2.4.            | Proper Start Control: Make go High 9 Proper Stop Control: Make go Low 9 Full-empty State Control and Observation 10 Data Control and Observation 10 Level Test and debug 10 Scan Shift 10 Non-Destructive Read of Circuit Signals 11 Non-Destructive Write of Circuit Signals 11 | )4<br>)7<br>)8<br>)0<br>)1<br>)7<br>0<br>1 |

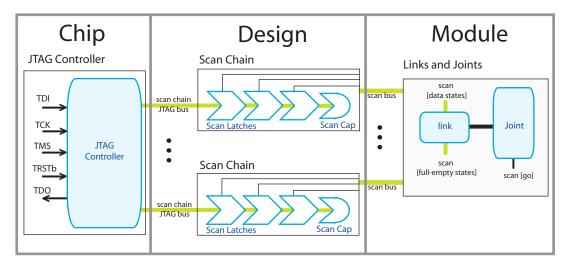

| 6 | 6.1.               | Module<br>6.1.1.<br>6.1.2.<br>6.1.3.<br>6.1.4.<br>Design<br>6.2.1.<br>6.2.2.<br>6.2.3.<br>6.2.4.<br>Chip Le | Proper Start Control: Make go High 9 Proper Stop Control: Make go Low 9 Full-empty State Control and Observation 10 Data Control and Observation 10 Level Test and debug 10 Scan Shift 10 Non-Destructive Read of Circuit Signals 11 Initialization at Power-Up 11               | )4<br>)8<br>)0<br>)1<br>)1<br>)1<br>(2     |

TABLE OF CONTENTS ix

| 7      | Arbi  | tration |                                                     | 121 |

|--------|-------|---------|-----------------------------------------------------|-----|

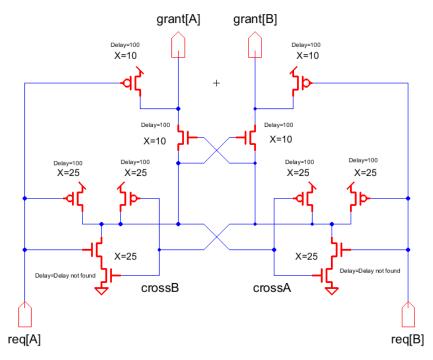

|        | 7.1.  | A Tale  | e of Two Arbiters                                   | 122 |

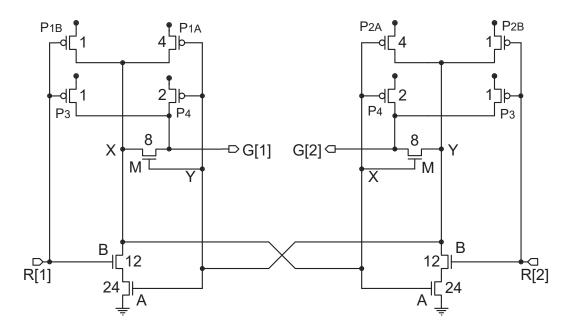

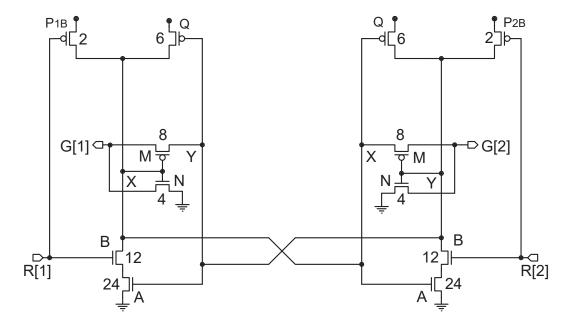

|        |       | 7.1.1.  | How the Arbiter Circuits Work                       | 124 |

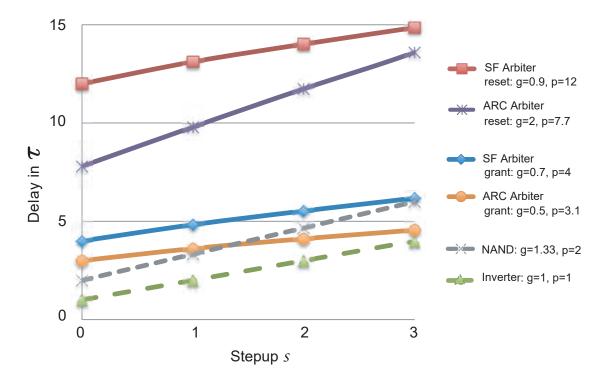

|        |       | 7.1.2.  | Least Uncontested Delay                             | 126 |

|        |       | 7.1.3.  | Our Simulation and Analysis                         | 126 |

|        | 7.2.  | Mathe   | ematical Analysis                                   | 127 |

|        |       | 7.2.1.  | Parameters: Load, Strength, Delay                   | 128 |

|        |       | 7.2.2.  | Overall Delay Analysis                              | 131 |

|        |       | 7.2.3.  | ARC Arbiter Analysis                                | 131 |

|        |       | 7.2.4.  | Sparsø-Furber (SF) Arbiter Analysis                 | 134 |

|        |       | 7.2.5.  | Mathematical Delay Analysis: Summary and Comparison | 136 |

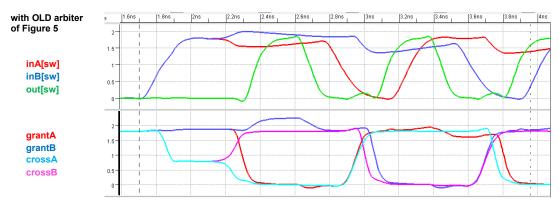

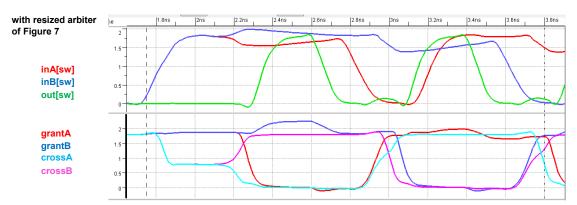

|        | 7.3.  | SPICE   | E Delay Simulations                                 | 138 |

|        | 7.4.  | Comp    | arison of Analyzed versus Simulated Results         | 141 |

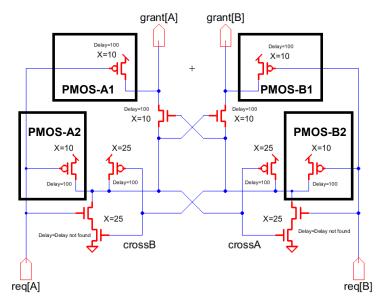

|        | 7.5.  | Sizing  | Validation from a Design Perspective                | 142 |

|        | 7.6.  | Sumn    | nary and Conclusion                                 | 146 |

|        | 7.7.  | Му Со   | ontributions for Chapter 7                          | 147 |

| 8      | Con   | clusior | n and Future work                                   | 149 |

| Re     | feren | ces     |                                                     | 153 |

| Аp     | pend  | lix A   | Telescope GasP: Storage and Broadcast               | 161 |

| Append |       | lix B   | Telescope GasP: Narrowcast                          | 195 |

| Аp     | pend  | lix C   | Telescope GasP: Repeat                              | 252 |

| Аp     | pend  | lix D I | Naturalized Communication and Testing               | 271 |

| Αp     | pend  | lix E   | Test Setup: Scan Chain Organization                 | 281 |

TABLE OF CONTENTS x

| Appendix F | Test Setup: JTAG Controller        | 300 |

|------------|------------------------------------|-----|

| Appendix G | Arbiter Design: Reduced Input Load | 342 |

| Appendix H | Arbiter Design: Noise Robustness   | 364 |

| Appendix I | Bonus: PhD Defense Presentation    | 376 |

LIST OF TABLES xi

# **List of Tables**

| Table 3.4.1: Path delay information for (T)GasP and Click modules 50         |

|------------------------------------------------------------------------------|

| Table 3.4.2: GasP timing information for Fibonacci number generator 51       |

| Table 3.4.3: Click timing information for Fibonacci number generator 52      |

| Table 7.2.1: Transistor equations for input capacitance versus strength 129  |

| Table 7.2.2: Equations for best transistor strengths for the ARC arbiter 133 |

| Table 7.2.3: Equations for best transistor strengths for the SF arbiter 135  |

| Table 7.2.4: Mathematically best strengths and uncontested grant delays 137  |

| Table 7.3.1: SPICE-simulated best strengths and uncontested grant delays 140 |

| Table 7.4.1: Comparison of analyzed versus simulated grant delays 141        |

LIST OF FIGURES xii

# **List of Figures**

| Figure 2.1.1: | An example of a FIFO using TGasP modules                | 11 |

|---------------|---------------------------------------------------------|----|

| Figure 2.2.1: | GasP Store circuit implementation                       | 14 |

| Figure 2.2.2: | GasP Store SPICE waveforms                              | 14 |

| Figure 2.2.3: | TGasP Amplify circuit implementation                    | 15 |

| Figure 2.2.4: | TGasP Amplify SPICE waveforms                           | 15 |

| Figure 2.4.1: | Second alternative TGasP Amplify circuit implementation | 20 |

| Figure 2.4.2: | Third alternative TGasP Amplify circuit implementation  | 20 |

| Figure 2.4.3: | Second alternative TGasP Amplify SPICE waveforms        | 21 |

| Figure 2.4.4: | Delay circuits to increase timing margins               | 22 |

| Figure 2.5.1: | Fast reset configuration for TGasP                      | 24 |

| Figure 2.5.2: | Fast reset SPICE waveforms for TGasP                    | 25 |

| Figure 3.1.1: | ARCwelder organization                                  | 32 |

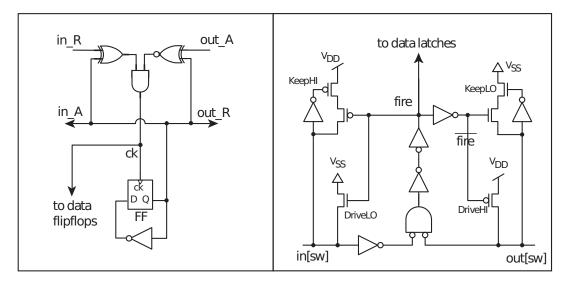

| Figure 3.2.1: | Store circuit implementations in Click and GasP         | 34 |

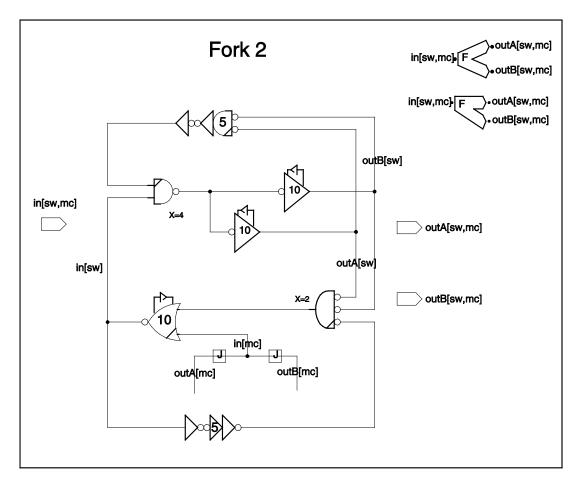

| Figure 3.2.2: | Fork circuit implementation in Click and GasP           | 37 |

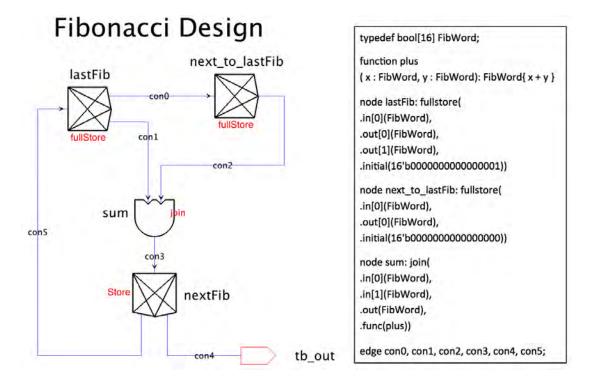

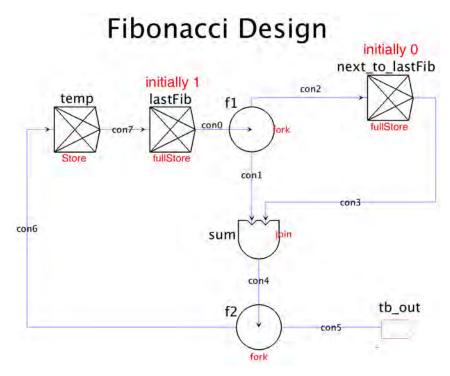

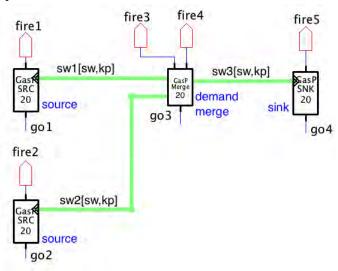

| Figure 3.3.1: | GUI design for Fibonacci number generator               | 40 |

| Figure 3.4.1: | GUI alternative design for Fibonacci number generator   | 49 |

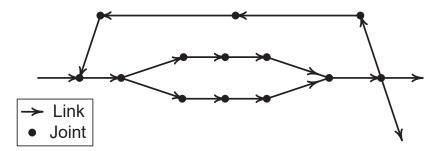

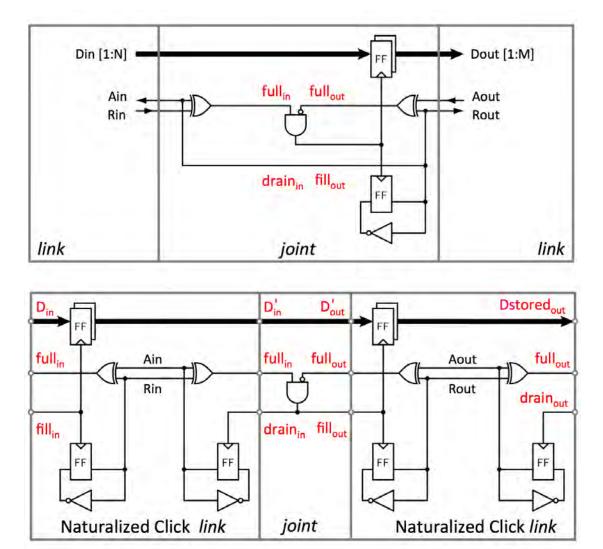

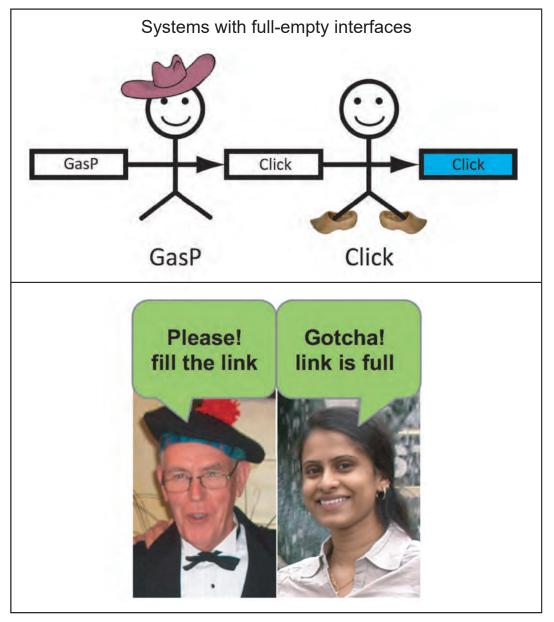

| Figure 4.0.1: | A self-timed dataflow system with links and joints      | 56 |

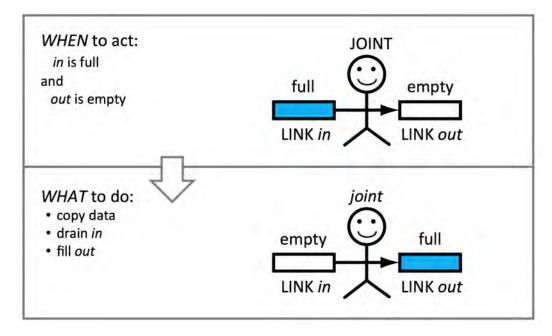

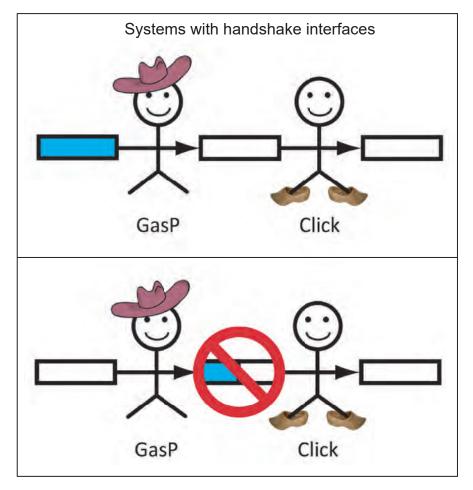

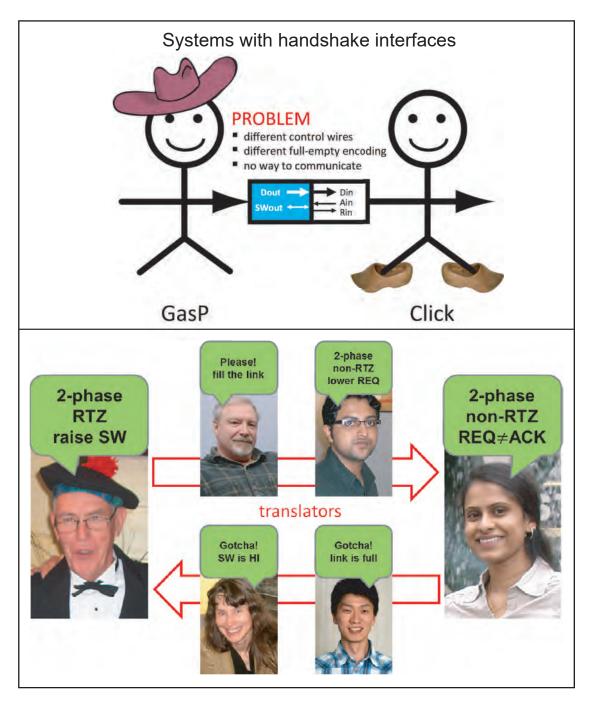

| Figure 4.1.1: | Pictorial representation of a self-timed FIFO           | 57 |

LIST OF FIGURES xiii

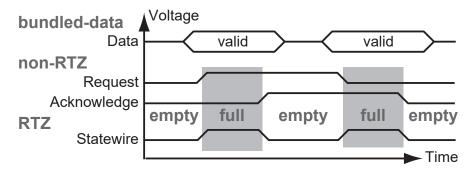

| Figure 4.1.2: | Full-empty representations for two-phase handshake protocols          | 59 |

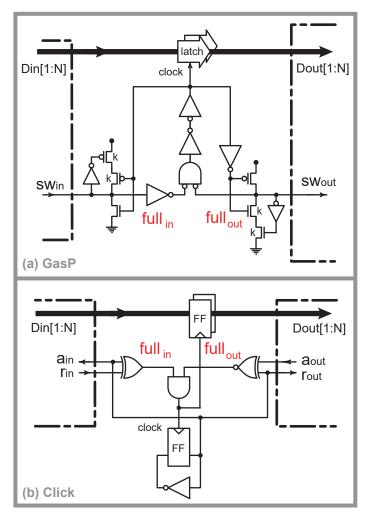

|---------------|-----------------------------------------------------------------------|----|

| Figure 4.1.3: | Original self-timed FIFO circuit in GasP and Click                    | 59 |

| Figure 4.1.4: | Pictorial view of a FIFO with GasP and Click modules                  | 61 |

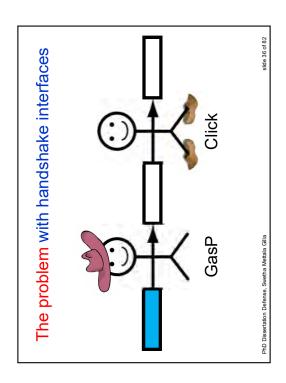

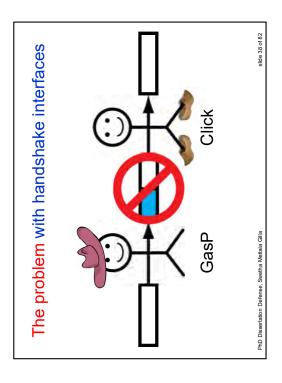

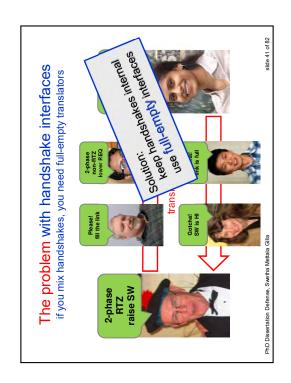

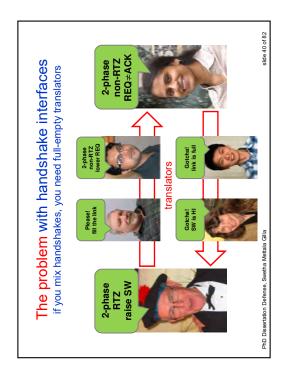

| Figure 4.1.5: | Mixed systems with handshake interfaces need translators              | 62 |

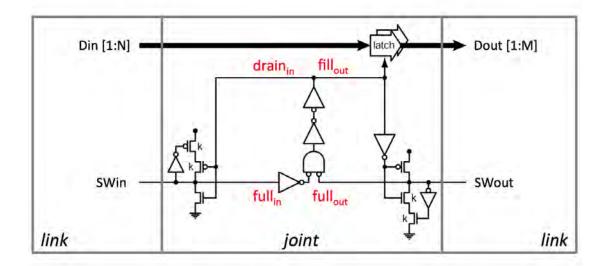

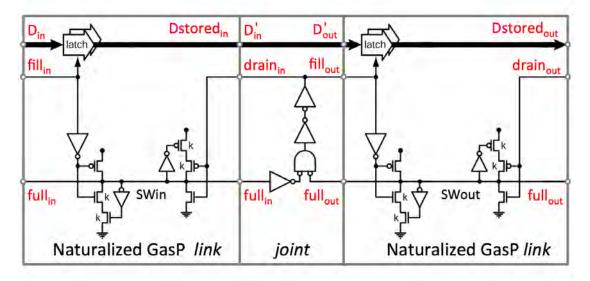

| Figure 4.2.1: | GasP circuit with full-empty interface                                | 64 |

| Figure 4.2.2: | Click circuit with full-empty interface                               | 65 |

| Figure 4.2.3: | Pictorial view of a mixed FIFO with full-empty interfaces             | 66 |

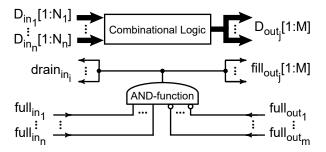

| Figure 4.2.4: | Design sketch of a naturalized broadcast joint                        | 68 |

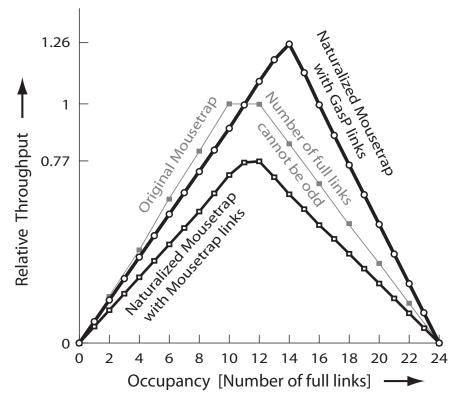

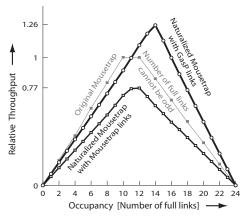

| Figure 4.3.1: | Canopy graph for original and naturalized designs                     | 69 |

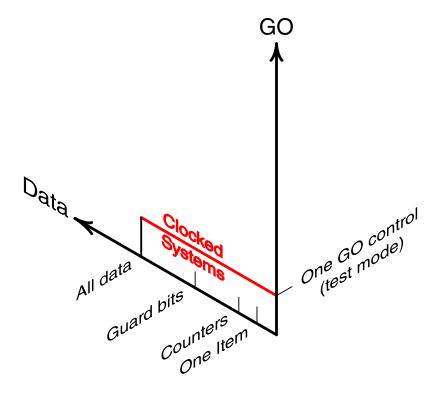

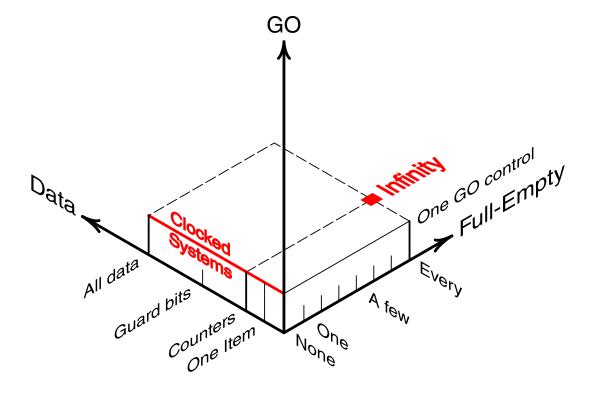

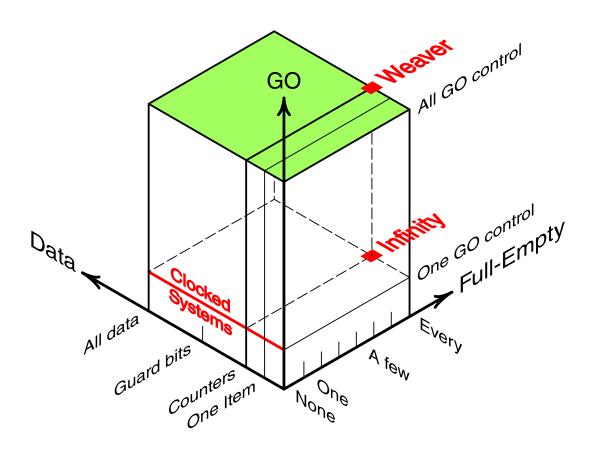

| Figure 5.1.1: | Where we came from: synchronous state-based test view                 | 74 |

| Figure 5.1.2: | Where we are: state-based test view applied to self-timed             | 75 |

| Figure 5.1.3: | Where we go: state- and action-based test view for self-timed         | 76 |

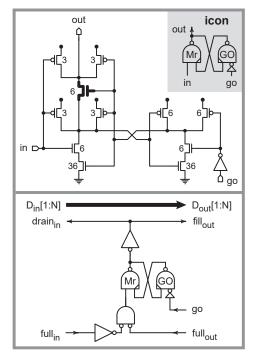

| Figure 5.2.1: | GasP circuit with MrGO                                                | 79 |

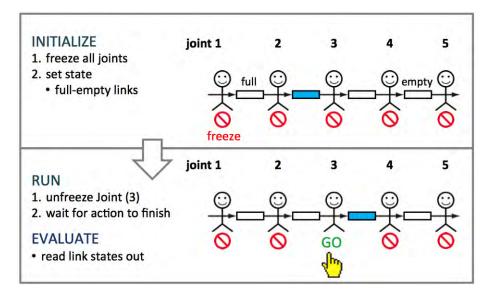

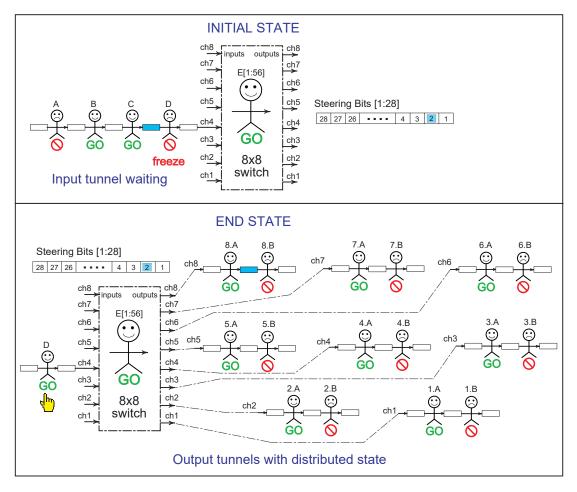

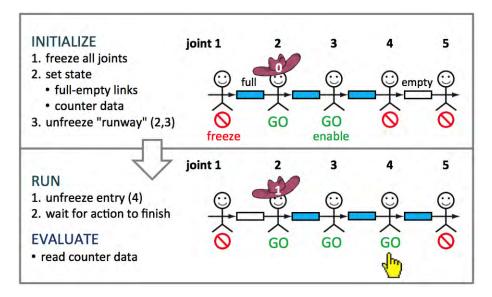

| Figure 5.3.1: | Pictorial representation of a one-shot test of a selected joint       | 81 |

| Figure 5.3.2: | A series of one-shot tests to prime a marginal latch test             | 82 |

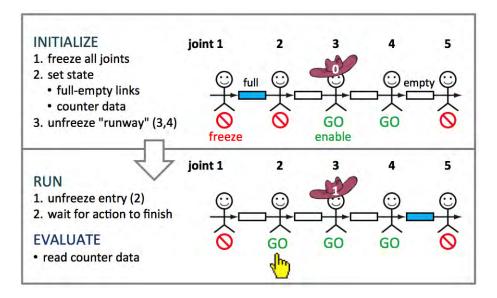

| Figure 5.3.3: | Pictorial representation of a breakpoint test                         | 82 |

| Figure 5.3.4: | Pictorial representation of an at-speed test with a single data item. | 83 |

| Figure 5.3.5: | Textual representation of an at-speed test with a single data item    | 83 |

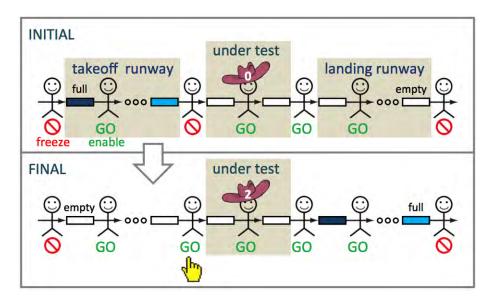

| Figure 5.3.6: | Pictorial representation of an at-speed test with a burst of data     | 85 |

| Figure 5.3.7: | At-speed test of a marginal latch using a burst of data items         | 85 |

| Figure 5.3.8: | Pictorial representation of an at-speed test for bubbles              | 86 |

| Figure 5.3.9: | Textual representation of an at-speed test for bubbles                | 86 |

| Figure 5.3.10 | : Test outline for exhaustive testing of stuck-at faults              | 87 |

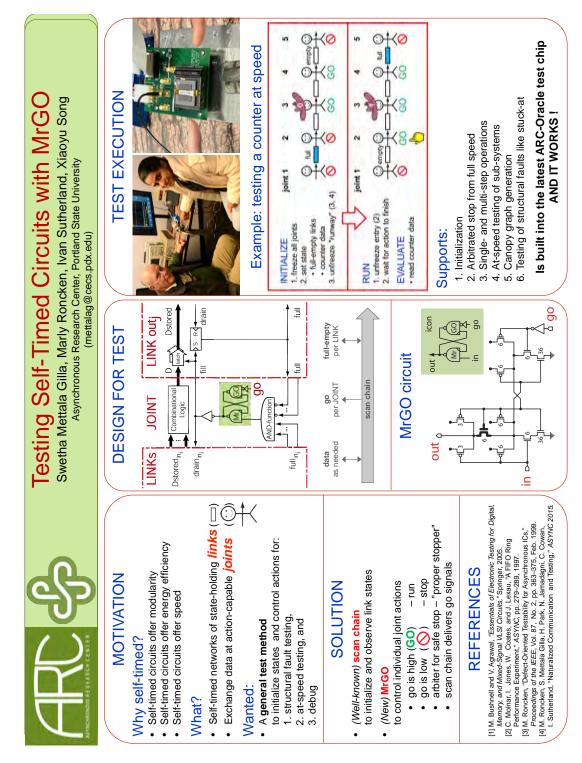

| Figure 5.5.1: | Poster, illustrating the test solution with MrGO                      | 89 |

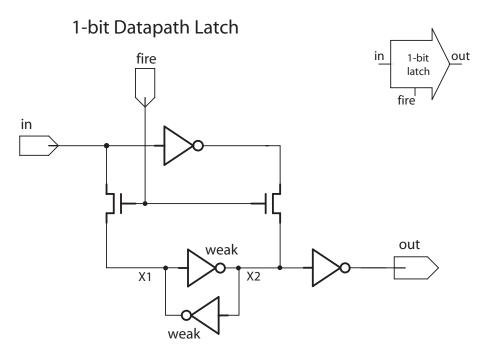

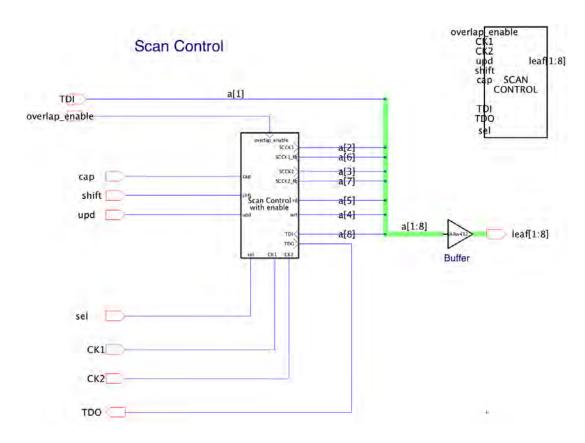

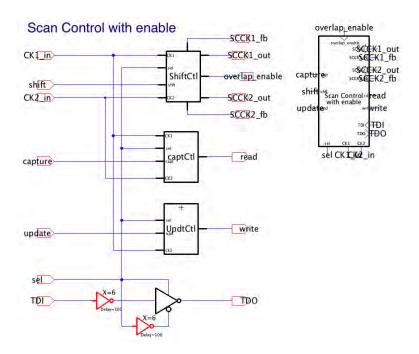

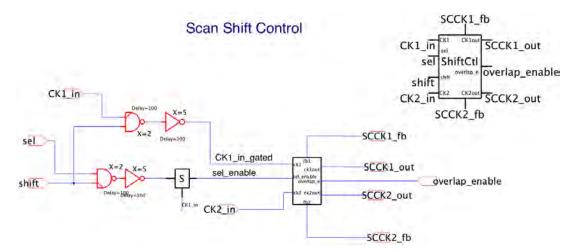

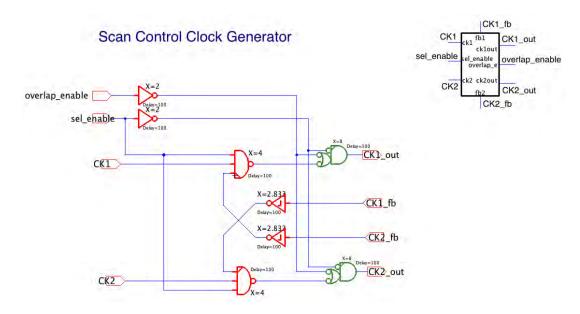

| Figure 6.0.1: | Block diagram of the hierarchical design for test approach            | 92 |

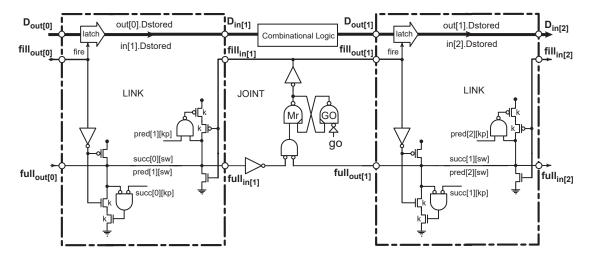

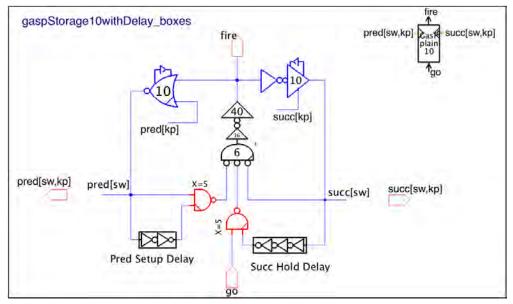

| Figure 6.1.1: | GasP FIFO implementation as links and joints with test signals        | 95 |

LIST OF FIGURES xiv

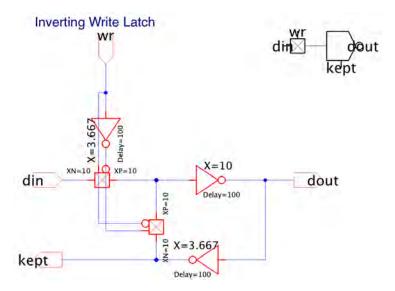

| Figure 6.1.2: | Transistor level schematic for a 1-bit datapath latch                |

|---------------|----------------------------------------------------------------------|

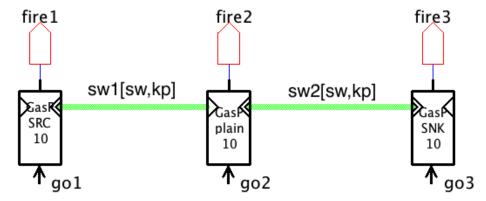

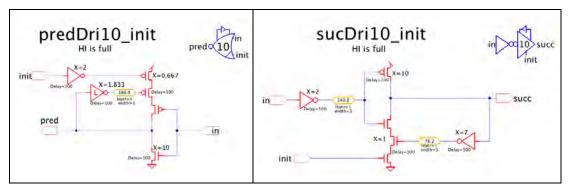

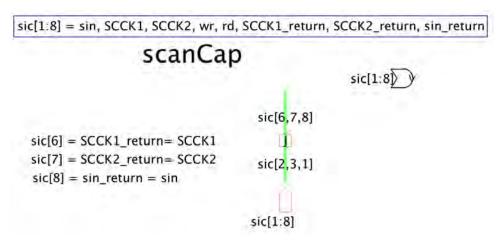

| Figure 6.2.1: | Pictorial representation of a GasP FIFO with scan chains 103         |

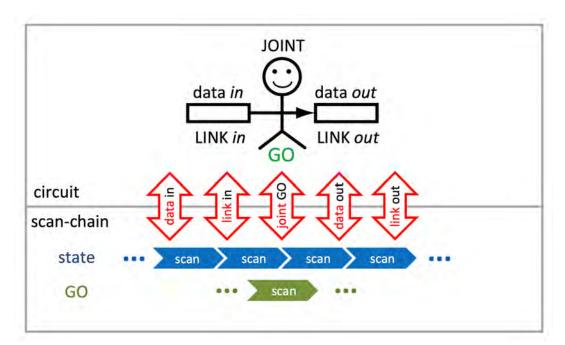

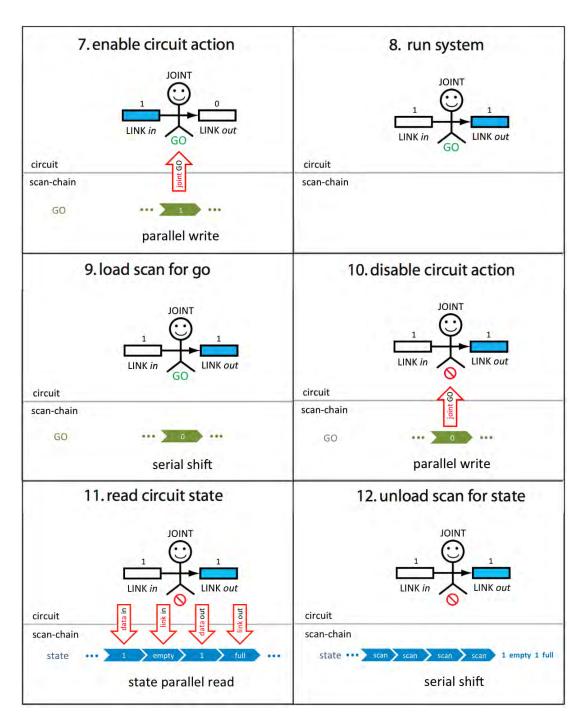

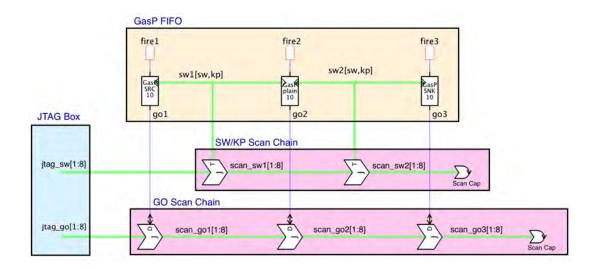

| Figure 6.2.2: | Scan operations for a one-shot FIFO test                             |

| Figure 6.2.2: | Scan operations for a one-shot FIFO test (continued) 105             |

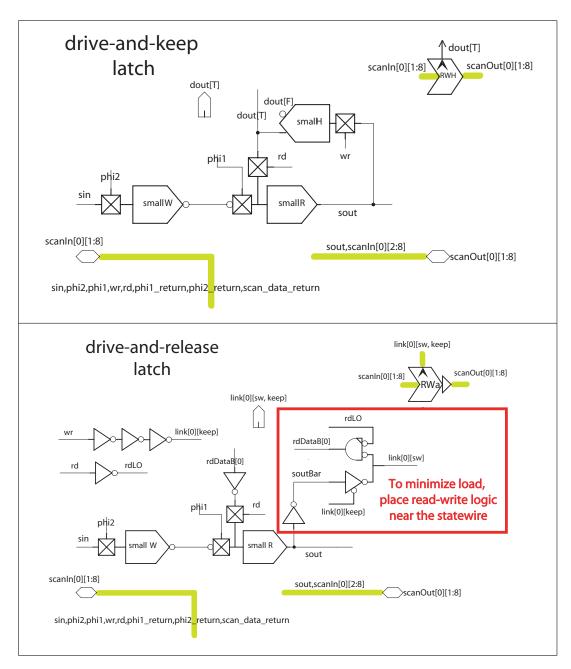

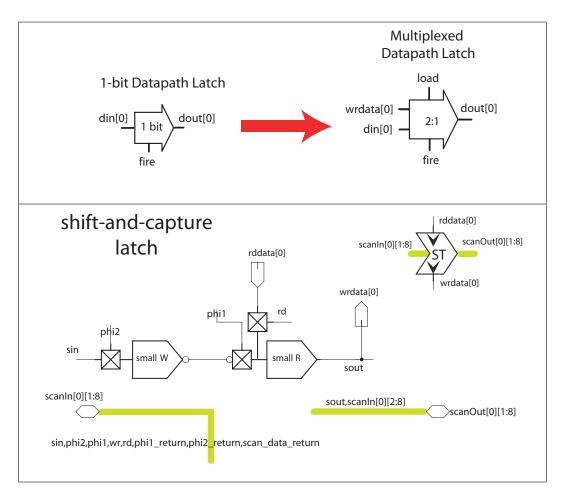

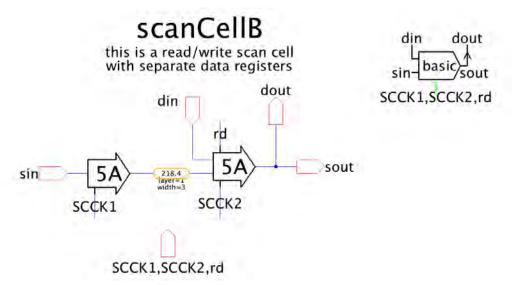

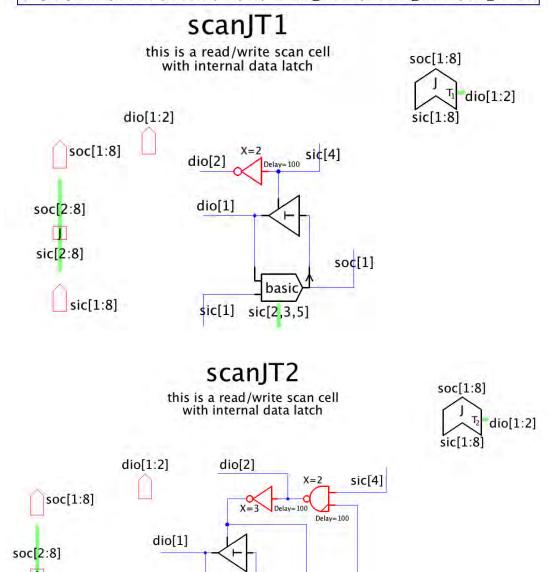

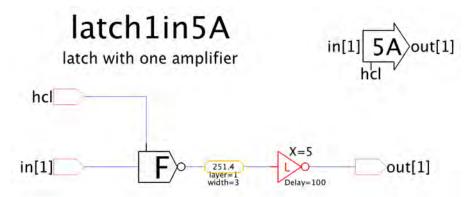

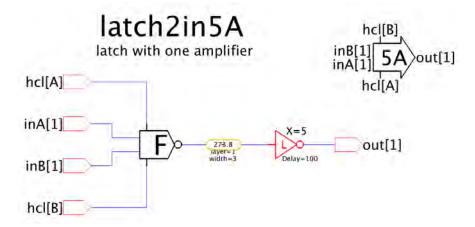

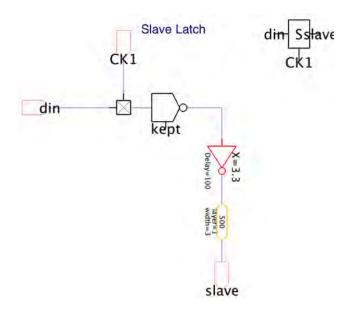

| Figure 6.2.3: | Scan segment implementations for GasP                                |

| Figure 6.2.4: | Scan segment implementations for GasP (continued) 109                |

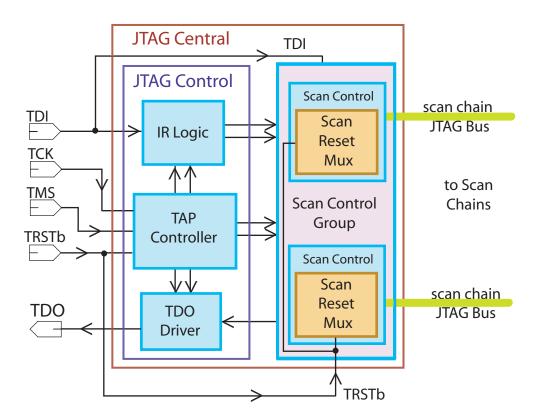

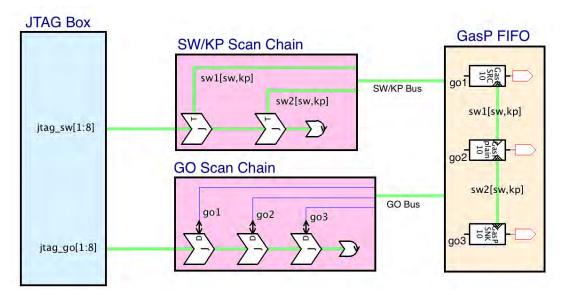

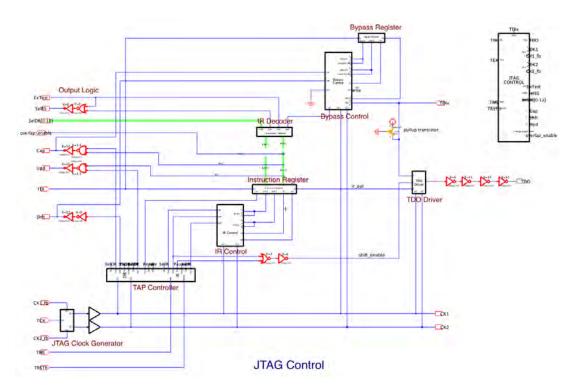

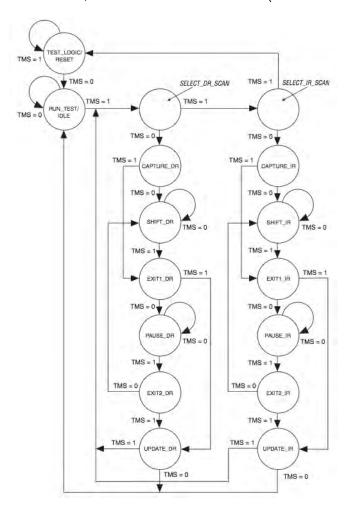

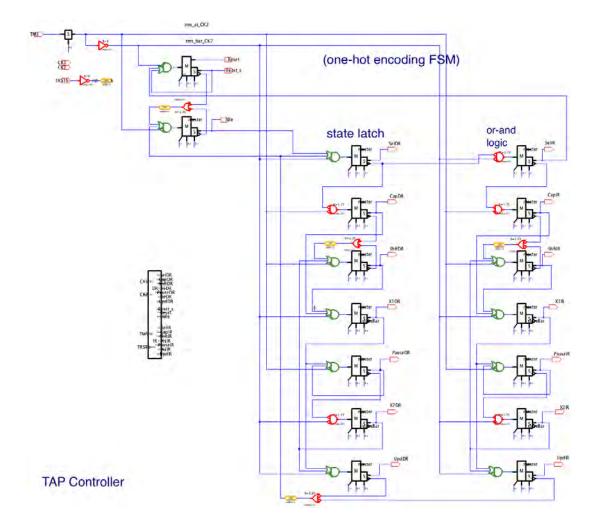

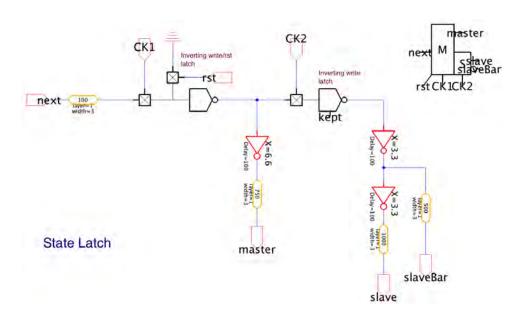

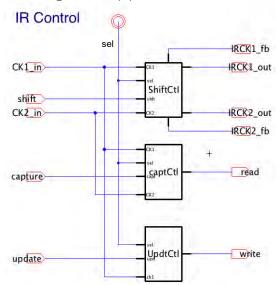

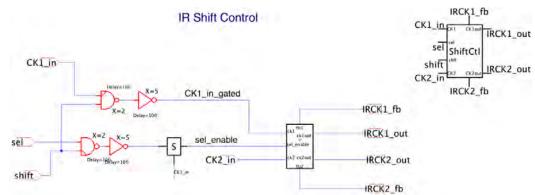

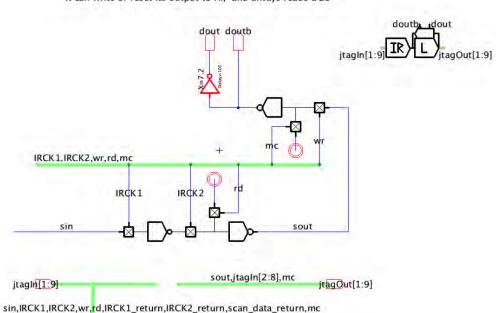

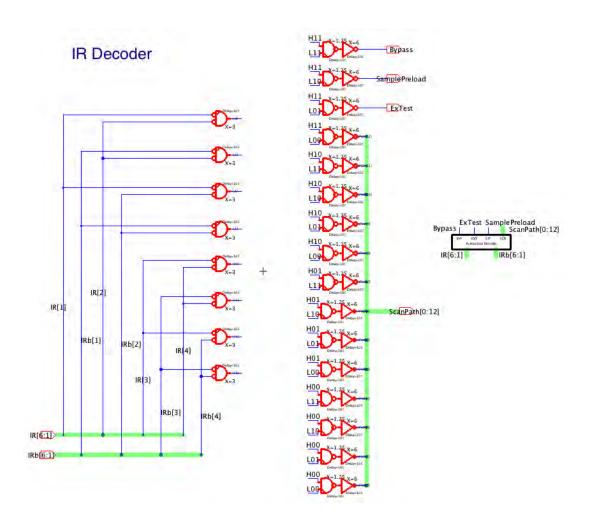

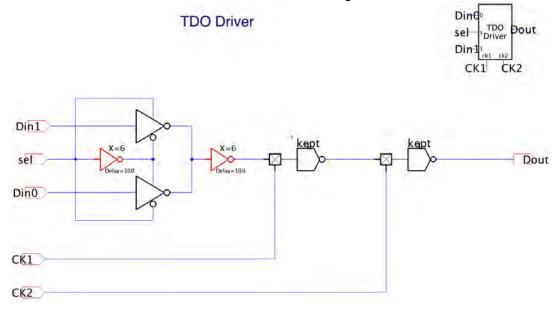

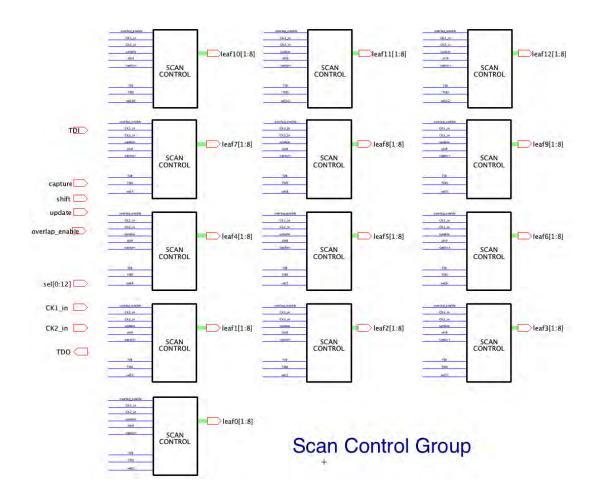

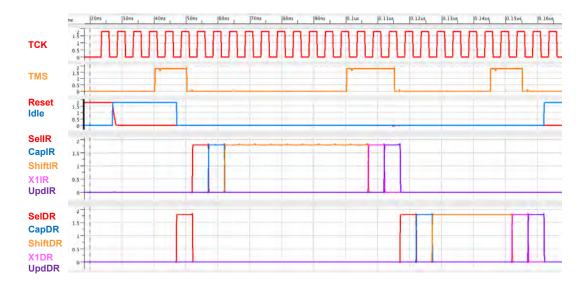

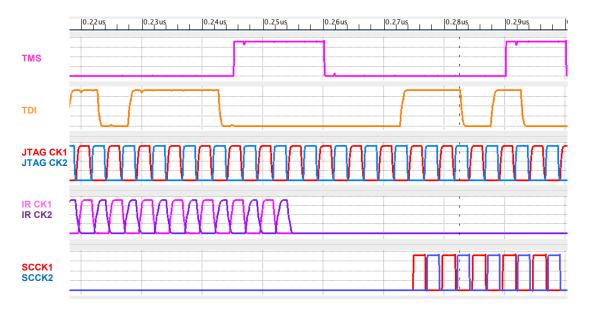

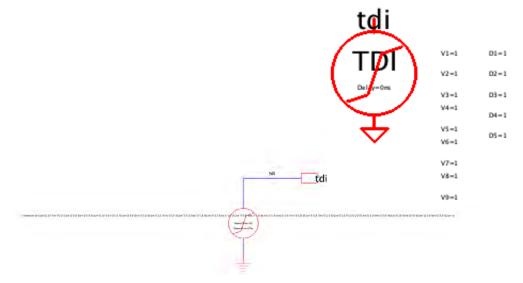

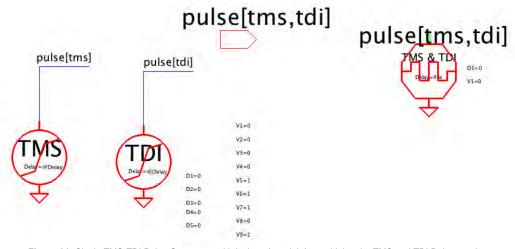

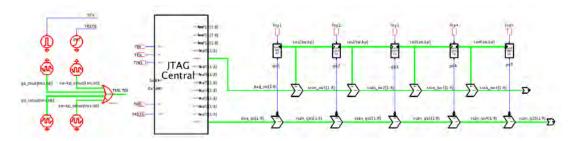

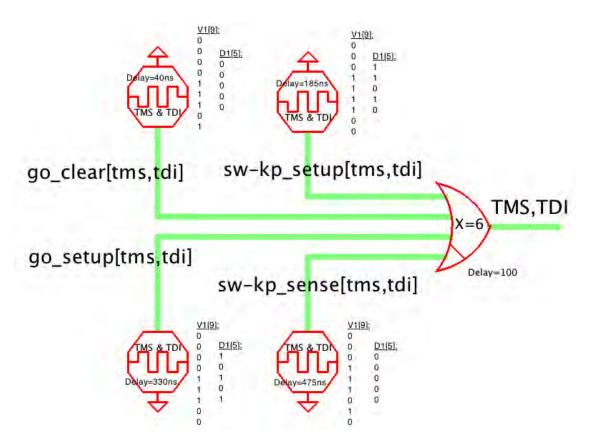

| Figure 6.3.1: | Block diagram of the JTAG controller                                 |

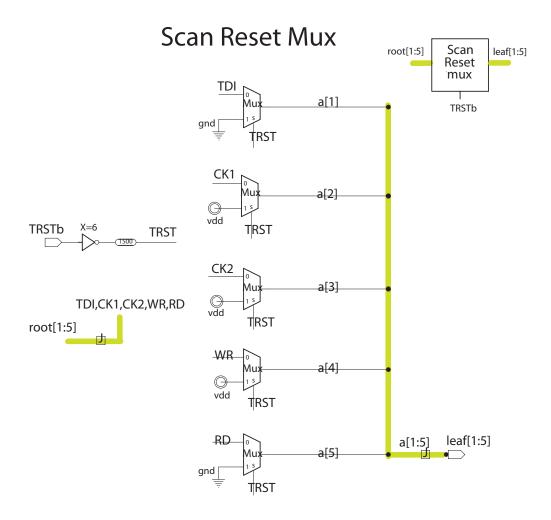

| Figure 6.3.2: | Scan Reset Mux module to support initialization at power-up 116      |

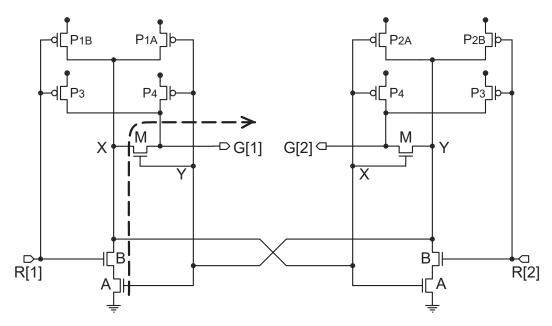

| Figure 7.1.1: | Transistor level schematic of the ARC arbiter                        |

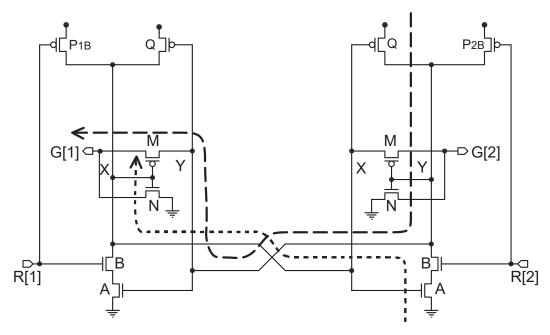

| Figure 7.1.2: | Transistor level schematic of the Sparsø-Furber (SF) arbiter 125     |

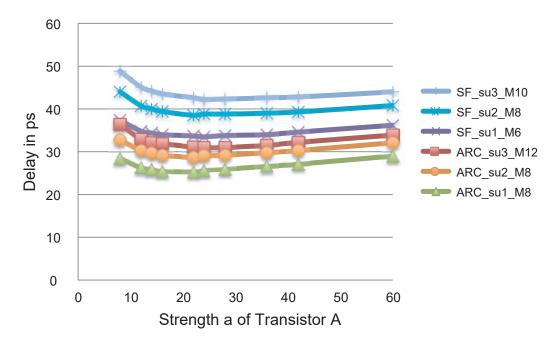

| Figure 7.3.1: | SPICE-simulated delay graphs for the two arbiters                    |

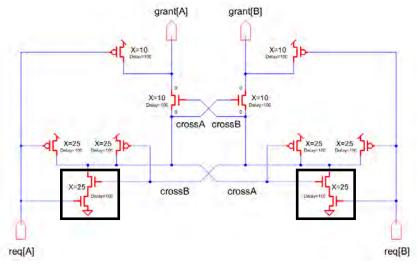

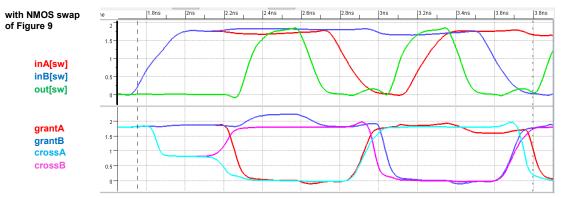

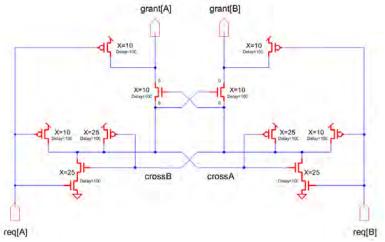

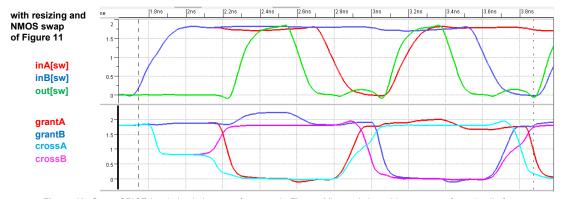

| Figure 7.5.1: | ARC arbiter with optimized strengths                                 |

| Figure 7.5.2: | SF arbiter with optimized strengths                                  |

| Figure 7.5.3: | Optimally sized arbiter graphs: grant, reset, and logical effort 145 |

1

## Introduction

Many modern computer systems are distributed over space. Well-known examples are Internet of Things and IBM's TrueNorth for Deep Learning applications. In clocked synchronous systems, large modern chips require multiple clock domains. High clock frequencies are possible only in limited-area clock domains [21]. Data synchronization between the clock domains is becoming increasingly onerous. At the Asynchronous Research Center (ARC) at Portland State University we build distributed hardware systems using self-timed computation and delay-insensitive communication. Self-timed design offers a way to coordinate actions between multiple time domains without using synchronizers. The flexibility provided by self-timed coordination makes it easier to change designs so they fit in a power or speed or time-to-market schedule. Self-timed design may be inevitable [54].

To make the design of self-timed systems practical, we must have automated design tools [7]. Current access to design automation tools for self-timed systems is very restrictive. Some of the best known tools are proprietary [5, 3]. Also, usage of the self-timed design paradigm is inhibited by difficulties related to testing [62]. Testing self-timed systems often requires dealing with combinational loops and distributed actions – both of which are handled poorly by standard tools for synchronous designs [59].

My PhD thesis focuses on both design compilation and test support for self-timed designs, particularly self-timed designs for dataflow applications. Both parts are necessary to go from self-timed circuits to large-scale hardware systems. The key insights resulting from this research have already led to generalizations and similar insights for other self-timed design approaches and tools [46].

## 1.1 Research Objective and Approach

#### **Objective**

The primary objective of this research is to provide generic design compilation and test support for self-timed circuits.

#### Approach

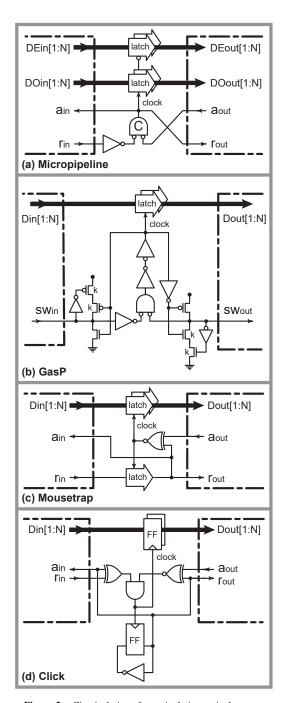

My research doesn't start from scratch. I use existing self-timed design families called GasP [55] and Click [43]. I use an existing design compiler tool called ARCwelder. I use existing scan test support approaches developed for testing synchronous designs and adapted for testing self-timed designs. My motivation for reusing these as my starting points is as follows.

- Click and GasP are excellent starting points for circuit design, because they are

the two extremes of so-called bundled-data self-timed circuit families with GasP

the most asynchronous and Click the most synchronous self-timed circuit style.

- 2. ARCwelder is an excellent starting point for design automation, because it compiles dataflow designs already into Click implementations. ARCwelder was built by Willem Mallon, a compiler and self-timed circuit expert, who based this compiler design on his prior knowledge and expertise as a core team member of Philips Handshake Solutions [43, 42].

Scan is an excellent starting point for test and test automation, because as ARC

researchers we have access to scan test software and hardware equipment used

by Sun-Oracle Laboratories to test GasP integrated circuits.

None of these three categories of starting points provide a generic design and test solution by themselves. But, together they can teach us where design and test automation procedures for Click and GasP differ and how we might introduce a new point of view to emphasize their same-ness in terms of design and test automation, while maintaining their uniqueness in terms of low power, high speed and latency tolerance.

#### 1.2 Research Summary

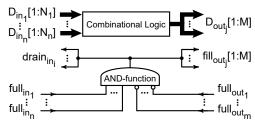

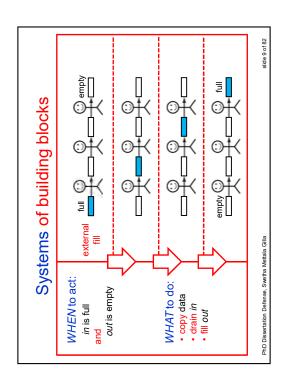

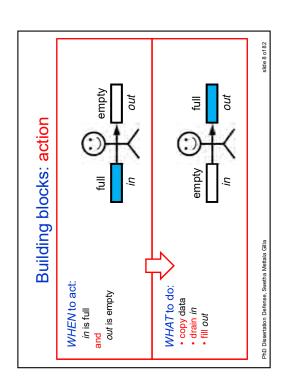

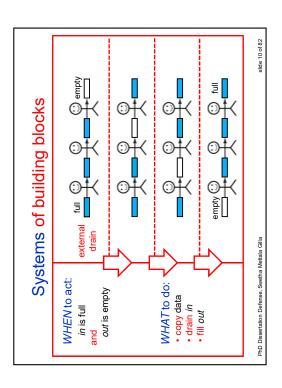

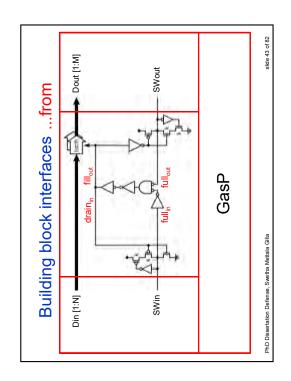

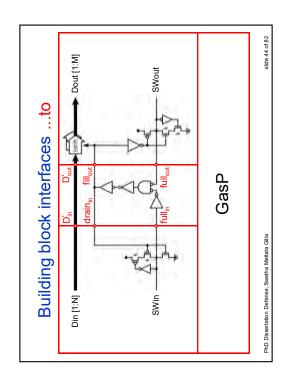

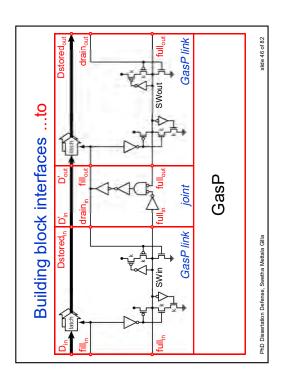

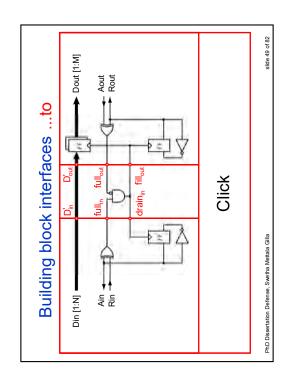

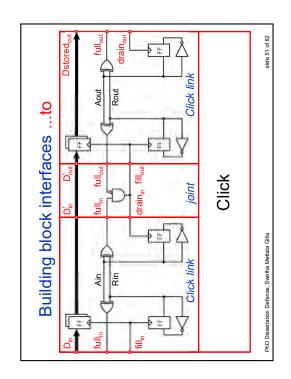

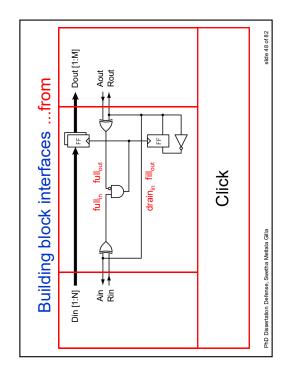

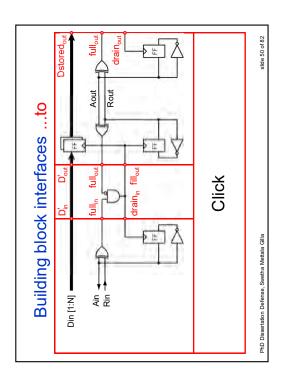

To compile a given dataflow design into self-timed circuits that are implemented using a GasP or a Click circuit design style, we partition the design into building blocks and provide a GasP or Click implementation for each building block.

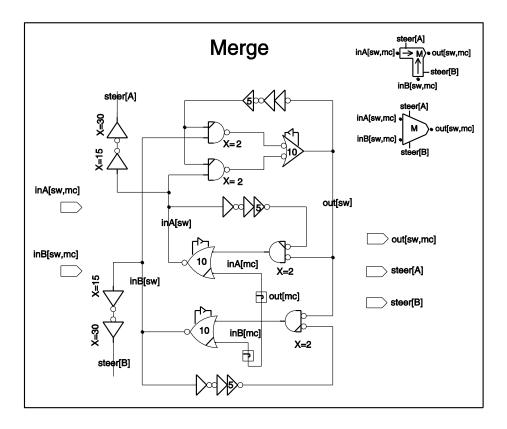

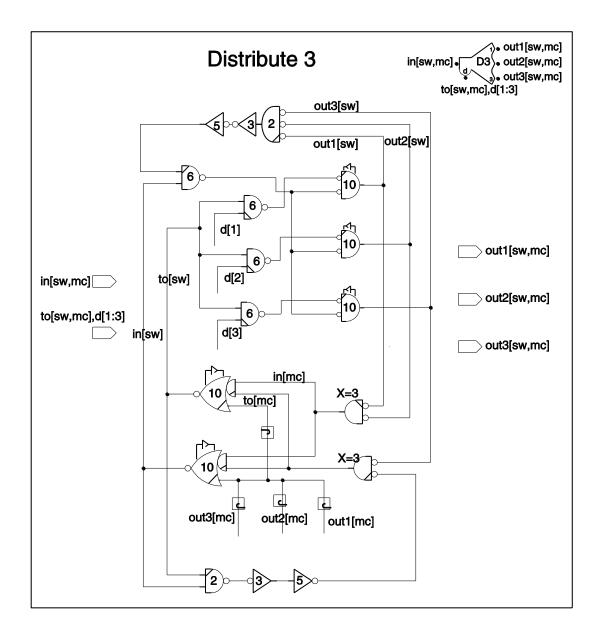

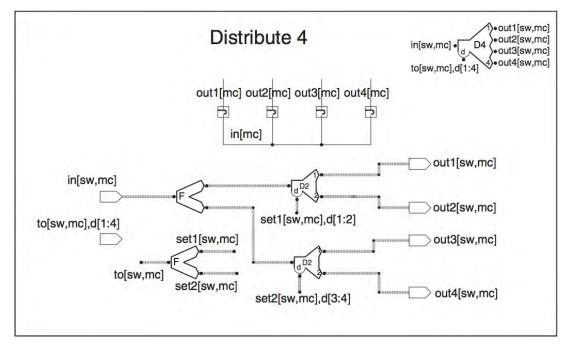

We have building blocks for buffering, data-driven selection, branch and merge operations, and so on. In GasP, all existing building blocks were fully pipelined, storing their own data. In Click, however, most of the building blocks that Willem Mallon had built into the ARCwelder compiler were pipelined only in their topological ordering, and few stored data. Willem separated building blocks into blocks for data storage and blocks for flow control. Willem called the blocks that store data "Storage modules." He called flow control blocks by their function, e.g. *Merge, Join, Fork*, and *Distribute*. Except for Storage modules, all other modules in ARCwelder refrain from storing data.

To compile the same ARCwelder dataflow designs in both Click and GasP, I developed a new collection of GasP modules. The new GasP modules implement flow control modules without storage for which Willem had a Click implementation in ARCwelder. I named

this new collection "*Telescope GasP*" — *TGasP* in short — because the communication behavior of the new modules resembles the folding and un-folding of a telescope.

In theory, all that the ARCwelder compiler must now support is a one-to-one mapping of dataflow building blocks, connected into a directed graph. Each building block is mapped to either a Click module implementation or a GasP or TGasP module implementation. In practice, this turned out to be more difficult than we had anticipated. Differences that we had expected to be minor, such as circuit initialization, and other differences that we had expected to be modular, such as communication protocol checks, incurred changes at multiple levels in the code and more code duplications than we felt were reasonable for a unified compiler solution. The documentation in this thesis shows where ARCwelder can be made more robust and more generic in supporting Click and (T)GasP designs.

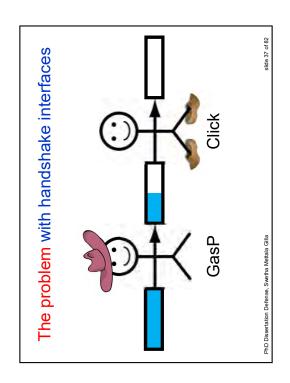

The unanticipated difficulties in reusing ARCwelder to compile dataflow designs into either Click or (T)GasP circuits served as an eye opener for how we, at our Asynchronous Research Center (ARC) and in the asynchronous research community at large, have created a "Tower of Babel" by using different communication protocols, different initialization schemes, and different design and test approaches.

As a result of my compiler study, we at the ARC started emphasizing the similarities between the various self-timed circuit families. In doing so, we created a new point of view that applies to the design and test of self-timed circuits in general [46]. This new point of view, will, I believe, also lead to a unified compiler solution for mapping dataflow designs into self-timed circuits of any style or mix of styles.

For the rest of my thesis research, I have worked out various parts related to the test solution presented in the 2015 publication by Roncken et al. [46]. The key to testing distributed systems, including self-timed systems, is to identify the actions in the system. In a distributed system there is no such thing as a global action. To test, debug,

characterize, and even initialize a distributed system, it is necessary to control the local actions individually! The designs that we develop at the ARC separate the actions from the states *ab initio*.

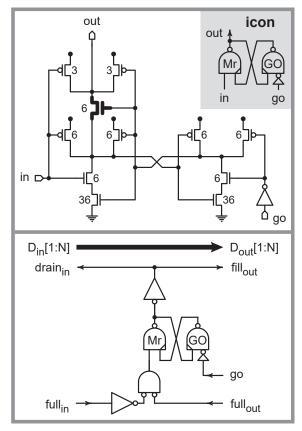

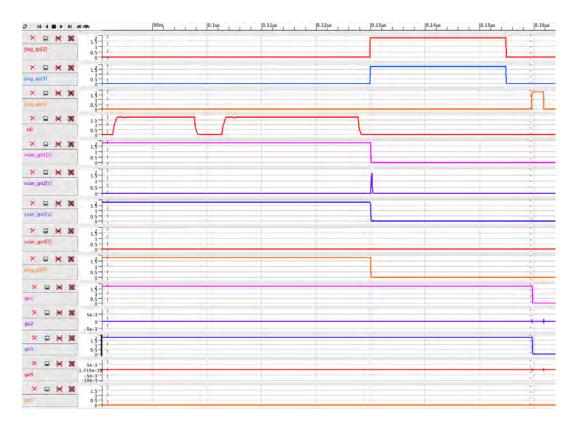

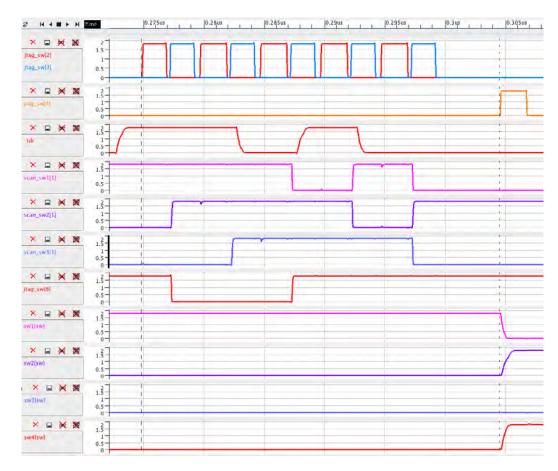

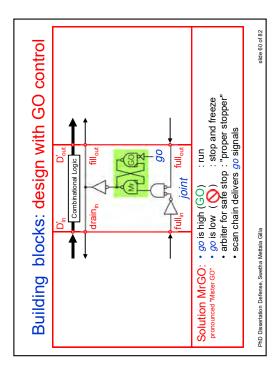

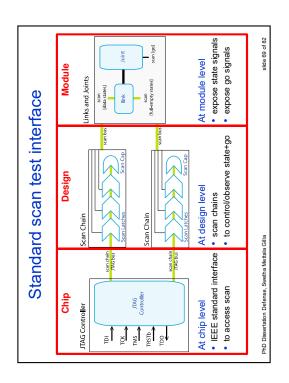

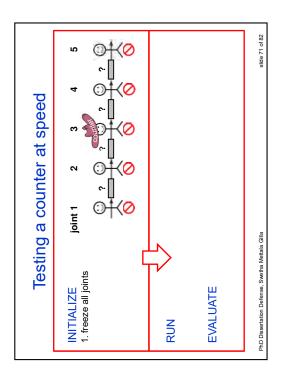

As part of my research in test and debug, I implemented a special circuit to control actions, called MrGO. I also developed a scan and JTAG test interface to take control over each individual and local action, each individual and local communication state, and any subset of data related state elements one might wish to control or observe. My test implementations keep the system's speed and power unchanged. They have been built into two silicon test experiments, called Weaver and Anvil, and were used successfully for test, debug, and performance characterizations.

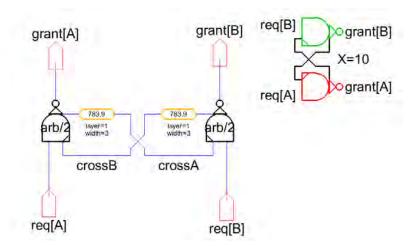

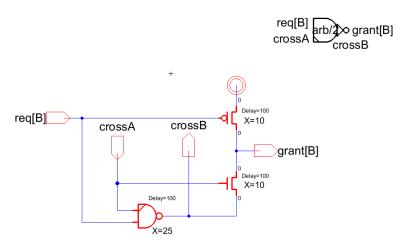

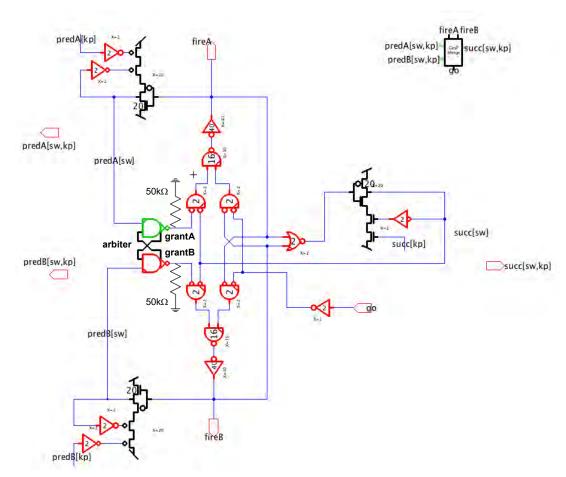

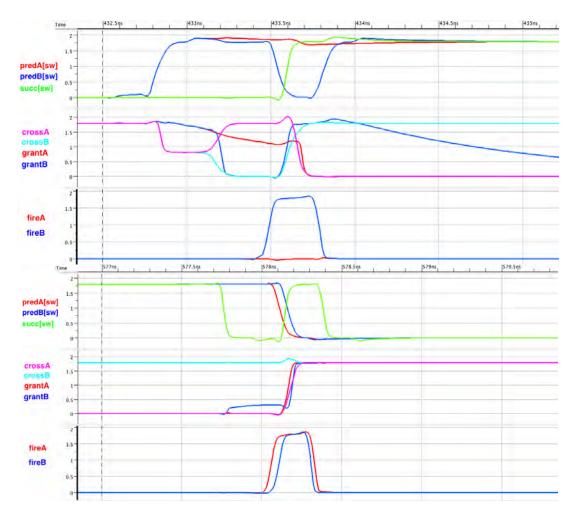

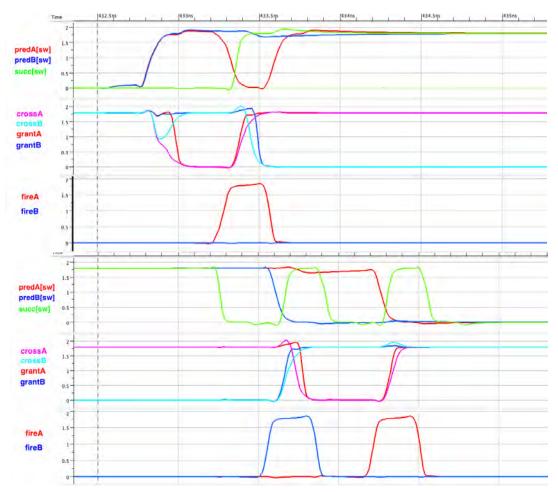

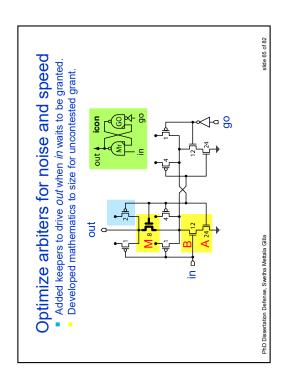

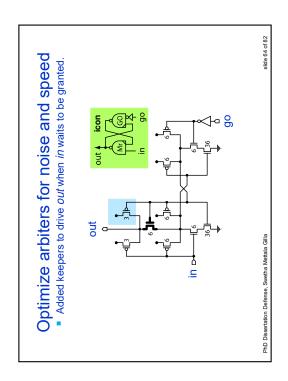

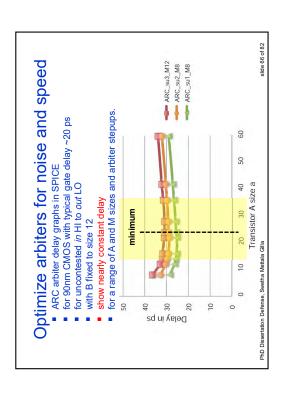

The special circuit for action control, MrGO, contains an arbiter. The presence of MrGO in each and every action has increased the number of arbiters in our designs dramatically. Where before we used arbiters only to solve access to shared resources, we now use arbiters in each and every basic computation cycle. Every self-timed action now has an arbitrated MrGO circuit. To develop a good MrGO implementation it is essential to design a fast and efficient arbiter. I have done extensive research on arbiter designs. I improved the existing ARC arbiter, making it efficient and robust. I also analyzed and compared the ARC arbiter design that we use as the basis for MrGO to the arbiter design used by the majority of self-timed circuit designs elsewhere. My analysis gives great insight into the role of the various transistors in both arbiter designs and how to size them for optimum performance.

## 1.3 My Contributions

While most of this thesis is joint work with my supervisors, the following key contributions are largely mine.

- The design and implementation of the Telescope GasP or TGasP family presented in Chapter 2 of this thesis, including the broadcast, narrowcast and repeat modules in Appendices A, B, and C.

- The development of a working scan design and JTAG test interface for GasP presented in Chapter 6 and Appendices E and F.

- The implementation of MrGO the special circuit that allows us to control actions for initialization, test, debug, and characterization and more recently mixed synchronous-asynchronous circuit operation [45].

- The development of a series of arbiter designs with lower input load and noise sensitivity, presented in Appendices G and H.

- The delay analysis and optimization in Chapter 7 of the ARC arbiter as used in MrGO, and of an alternative arbiter commonly used outside the ARC and referenced in the Sparsø-Furber book [50].

## 1.4 Thesis Organization

The rest of this thesis is organized as follows.

Chapter 2 introduces Telescope GasP or TGasP. TGasP modules supplement the already existing or "traditional" GasP modules. Together, GasP and TGasP form a

complete backend for the existing ARCwelder compiler developed by Willem Mallon. This backend is complete in the sense that it serves as a replacement for the existing backend in Click. All previous dataflow designs in ARCwelder can be mapped to Click or to circuit implementations with GasP and TGasP modules. I discuss the design differences between Telescope GasP and traditional GasP. I also show various ways to design TGasP circuits and their pros and cons. A representative set of TGasP modules with correctly sized designs and SPICE simulations can be found in the ARC reports shown in Appendices A, B, and C.

Chapter 3 discusses our self-timed dataflow design and compilation flow and the ARCwelder compiler. I explain key differences between the Click and GasP circuit families. I explain the various steps involved in extending the ARCwelder compiler to compile dataflow designs into both Click and GasP circuit implementations.

#### Note

The ARCwelder compiler research and experimental results from Chapter 3 have changed the point of view on self-timed design and test at the ARC. The new design point of view is included in my thesis in Chapter 4. The new test point of view is included in my thesis in Chapter 5.

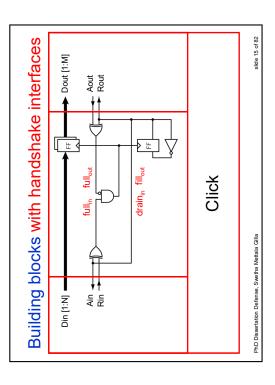

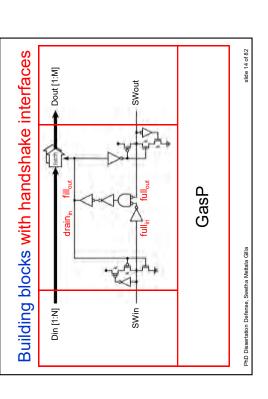

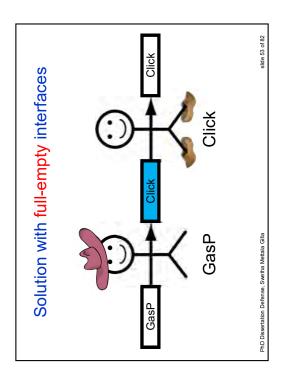

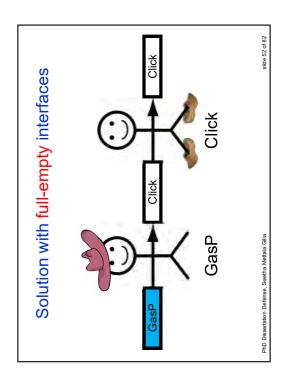

• Chapter 4 introduces the ARC's new point of view on self-timed design [46]. This new design point of view applies to all self-timed circuit families and makes it possible to mix, match, reuse, and exchange designs from different circuit families without further translation. The new approach, dubbed "Naturalized Communication," makes computation as important as communication from the lowest levels of design and up. As a result, the specifics of the various communication protocols and data storage solutions can be hidden inside the design modules, and modules can interact using common, generic interfaces.

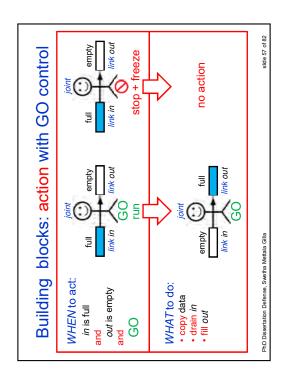

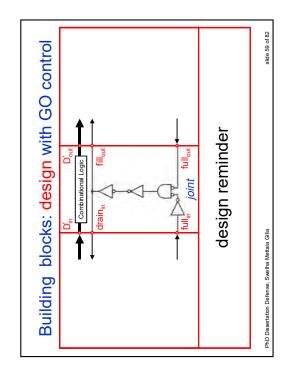

• Chapter 5 introduces the ARC's new point of view on initialization and testing of self-timed designs [46]. This new point of view applies to all self-timed circuit families and distributed systems. The new approach, dubbed "Naturalized Testing," makes actions as important as states, from the lowest levels of design-for-test and up. In addition to scan design-for-test circuitry to manage state, we add go signals and MrGO circuitry to manage actions. Chapter 5 describes various test experiments using MrGO and scan.

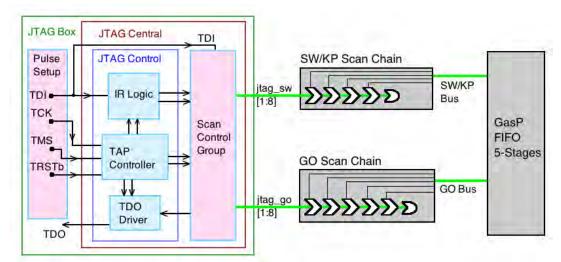

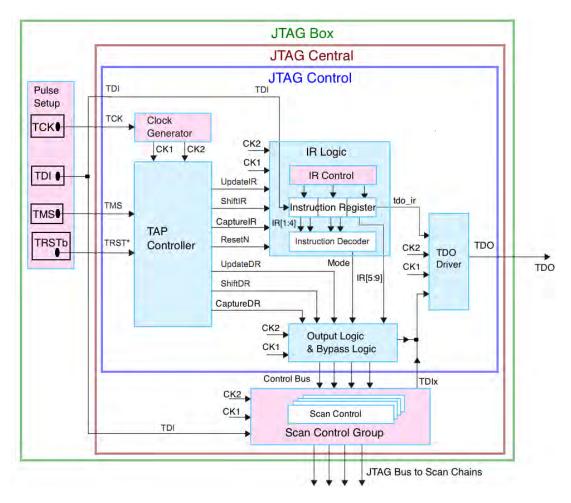

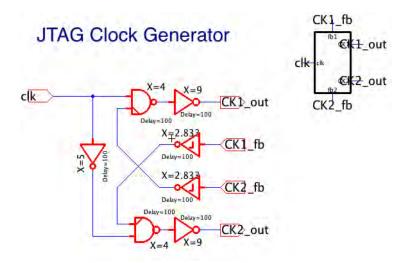

- Chapter 6 gives an overview of hierarchical design-for-test implementations from standard external test interfaces to the specific management of (1) distributed states via traditional scan test circuits and (2) distributed actions via the new MrGO circuitry. Supporting documentation for Chapter 6 with specific implementation details can be found in Appendices E and F.

- Chapter 7 focuses on arbiter designs and compares the ARC arbiter and the Sparsø-Furber arbiter [50]. Supporting documentation for Chapter 7 can be found in Appendices G and H.

- Appendices A, B, and C provide additional details to Chapter 2, Appendix E and Appendix F provide additional details to Chapters 5–6, and Appendices G and H provide additional details to Chapter 7.

- Appendix D gives the IEEE publication "Naturalized Communication and Testing,"

published at ASYNC 2015, to which my PhD thesis was instrumental, and which

vice versa was instrumental to this thesis.

- Appendix I contains the slides of my PhD dissertation defense, presented on the 3<sup>rd</sup> of November, 2017. Reading this 4-slides-per-page handout may be the quickest way to get a tour of this thesis. I hope you will enjoy the tour!

# Telescope GasP (TGasP)

This chapter gives the rationale for using Telescope GasP (TGasP) implementations for pipeline modules used in ARCwelder [18]. ARCwelder is a design and compilation environment for self-timed dataflow computations. The software for ARCwelder was developed by Willem Mallon at Portland State University between 2010 and 2012. The organization of ARCwelder builds upon results and key lessons learned from the self-timed data-driven compiler effort by Handshake Solutions [43].

The term "telescope," introduced in this thesis, refers to the communication behavior of a pipeline with telescope modules. The forward extension by communication channels with *valid data* and the reverse shortening by communication channels with *no-longer-valid or irrelevant data* are reminiscent of the extension (unfolding) and shortening (folding) of a jointed telescope with sliding tubes — see also Figure 2.1.1. This is particularly obvious for modules with a single data input and a single data output channel:

- (unfold) A handshake on the input starts a handshake on the output channel.

- (fold) After the output handshake completes, the input handshake completes.

## 2.1 Why Telescope GasP?

The modules in Willem Mallon's version of ARCwelder are Click modules [18] and most of them use the telescopic handshake relation described earlier, as do most of the original handshake components used by Philips Handshake Solutions [60, 50, 43]. We use Telescope GasP Modules to have a GasP version for such "Telescope Click" modules.

Telescopic handshakes can be used, for instance, to avoid intermediate data storage, which is the key reason why Willem Mallon incorporated them in ARCwelder. They can also be used to bridge long distances [10].

Wires that span a long distance often require amplification. Unidirectional wires, like data wires, can be amplified by inserting repeaters, i.e., buffers or pairs of inverters. Single-track statewires in GasP cannot be amplified using buffers or inverters because they are bi-directional. To amplify these single-track statewires we insert a Telescope GasP module with the following properties:

- The module behaves like a First In First Out (FIFO) buffer module.

- The forward latency in the control flow matches that in the repeated data wires.

The ASYNC 2011 publication by Jo Ebergen et al. [10] presents an design that behaves like a Telescope GasP FIFO module. Insertion of such a module helps reduce or even avoid the relaxation delays for long-range GasP communication that I presented at ASYNC 2010 [23] and which were also reported separately by Simon Hollis [12].

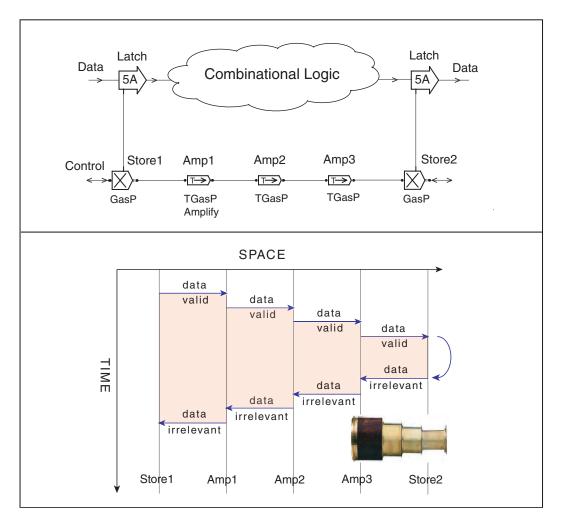

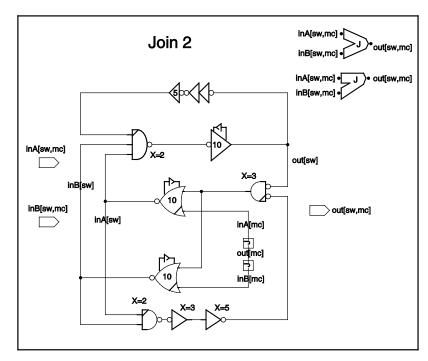

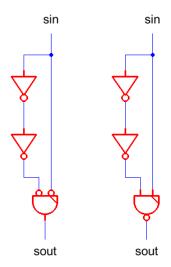

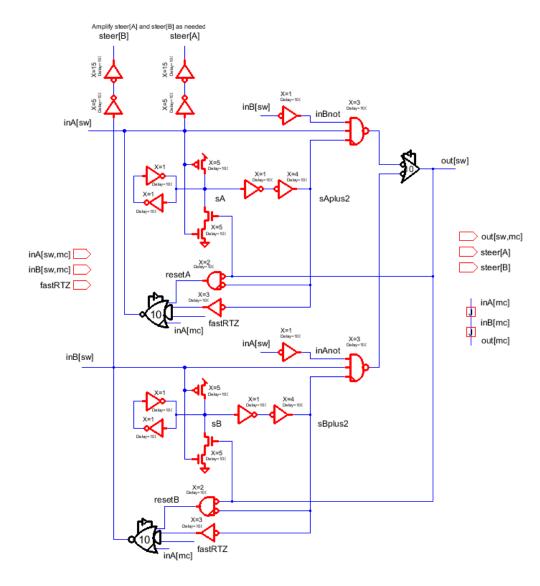

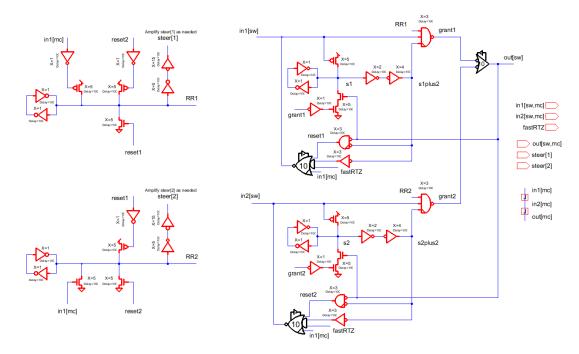

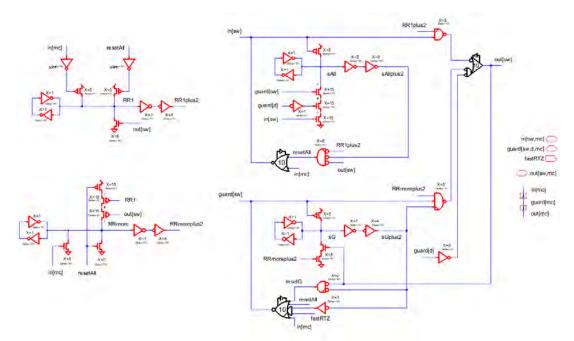

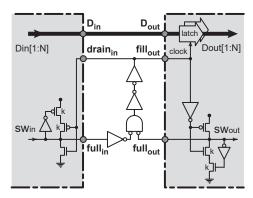

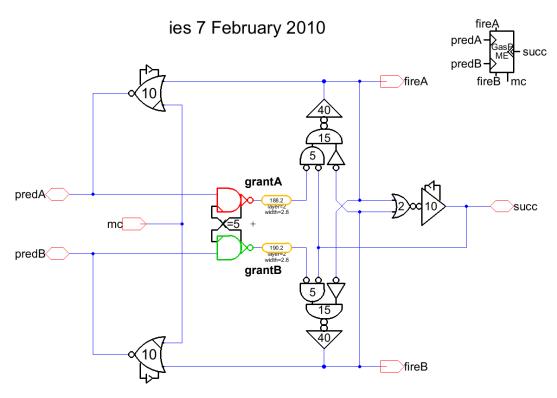

Figure 2.1.1(top) presents an example of a dataflow FIFO using Telescope GasP modules as repeater modules. Only the Store modules, *Store1* and *Store2*, control latches in the datapath. The Amplify modules, *Amp1* and *Amp2* and *Amp3*, control no data latches. To make this work, the data latch contents feeding the combinational logic must remain

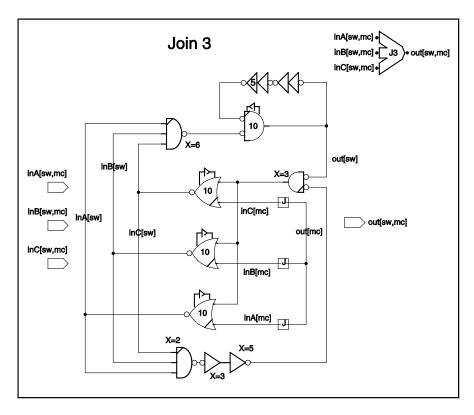

Fig. 2.1.1: (top) Example of a dataflow computation using TGasP Amplify modules. The picture shows the data latches and combinational logic at the top and the control part of the GasP and TGasP modules at the bottom. We assume that the delay through the latches and combinational logic is smaller than the delay through the control. Modules Store1 and Store2 are traditional GasP modules that allow their predecessors to fetch new data on their input channels while their successors process the data on their output channels. Modules Amp1, Amp2 and Amp3 are TGasP modules that keep their predecessors waiting, holding their data valid and stable, until their successors have stored the results of the combinational logic computation. (bottom) Space-Time diagram showing the telescopic handshake behavior of the Amplify modules. Note the forward extension of the handshake channels with valid data while the data are processed by the combinational logic between Store1 and Store2. Note the reverse shortening of these same channels with no-longer-valid or irrelevant data after the computed results are stored by Store2. This behavior is reminiscent of the extension (unfolding) and shortening (folding) of a jointed telescope with sliding tubes. As reference, a picture of a jointed telescope with sliding tubes has been inserted in the bottom-right corner. Notice its similarity to the shaded area in the Space-Time diagram.

stable until the latches fed by the combinational logic have captured the results. To meet this requirement, the Amplify modules keep their predecessors waiting, holding their data valid and stable, until their successors have stored the results of the combinational logic computation, as illustrated in Figure 2.1.1(bottom).

When the leftmost Store module in Figure 2.1.1, *Store1*, initiates a handshake to its successor, *Amp1*, Amplify module *Amp1* initiates a handshake to its successor module, *Amp2*, who then initiates a handshake to its successor, *Amp3*. Meanwhile, the data stored in *Store1* are processed by the combinational logic. After three amplifications, the handshake reaches the rightmost Store module, *Store2*. By the time the handshake reaches *Store2*, the results of the combinational logic computation have arrived at the latch inputs of *Store2*. Module *Store2* now captures these results in its latches, and releases the data-control bundling requirement for its predecessor, *Amp3*, which subsequently releases the bundling requirements for its predecessor, *Amp2*, and so forth, until the bundling requirement on the output channel of the leftmost Store module, *Store1*, is released. At this point, *Store1* may start a new handshake with new data.

Store modules, like *Store1* and *Store2* in Figure 2.1.1(top), are the only modules in ARCwelder that store data. They do so by clocking local latches or flipflops in the datapath. As such, Store modules can be used to isolate data computations and datapaths and to interface between different datapath computations. The non-Store modules in Figure 2.1.1 and in the ARC reports in Appendices A, B, and C avoid storing data and clocking latches or flipflops in the datapath.

The ARCwelder compiler lets the designer indicate explicitly when and where data are to be stored. The compiler checks that every loop in the dataflow graph has at least two Store modules; all other modules may be free of storage. ARCwelder also checks that data-control bundling requirements are met on a datapath per datapath basis, from the sending set of Store modules with latches feeding the combinational logic computations

in the datapath to the receiving set of Store modules with latches fed by the datapath. It is unnecessary to guarantee data-control bundling requirements on individual, intermediate channel connections. This makes it possible to use time-borrowing techniques to optimize datapaths in their entirety for speed and power [18].

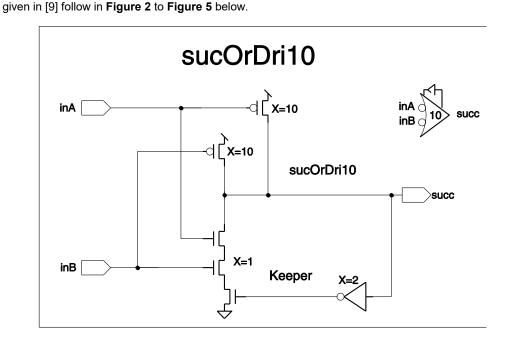

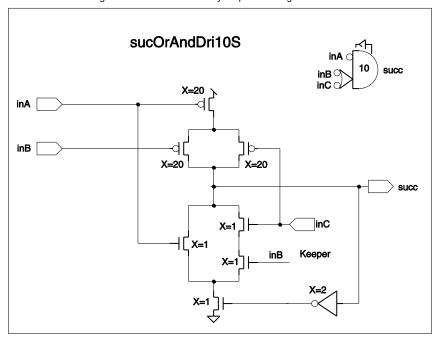

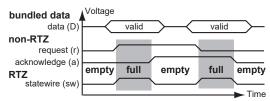

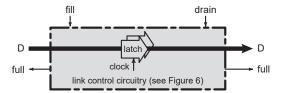

#### 2.2 Traditional versus Telescope GasP

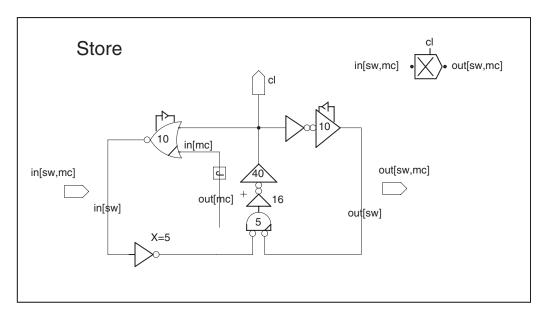

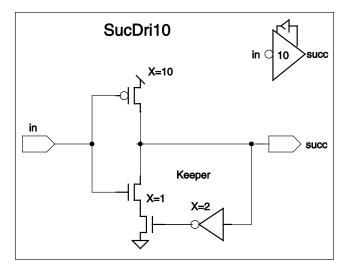

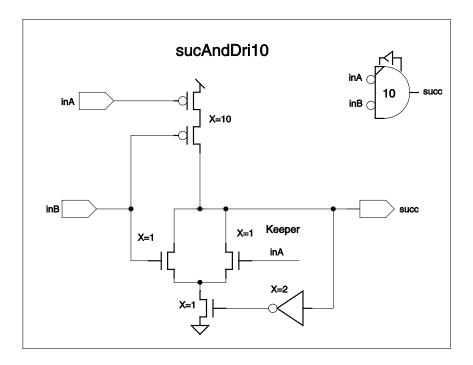

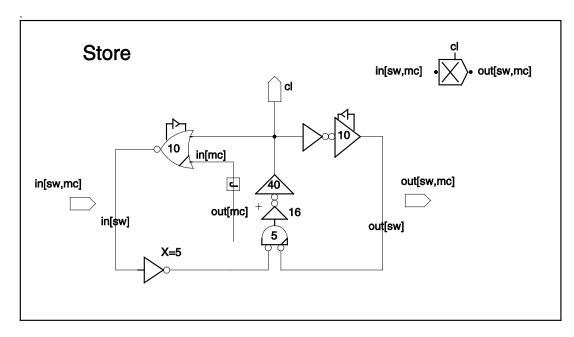

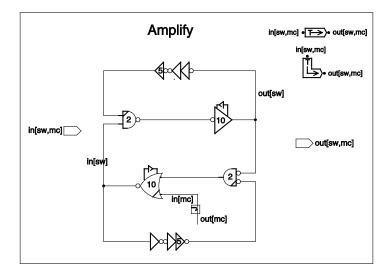

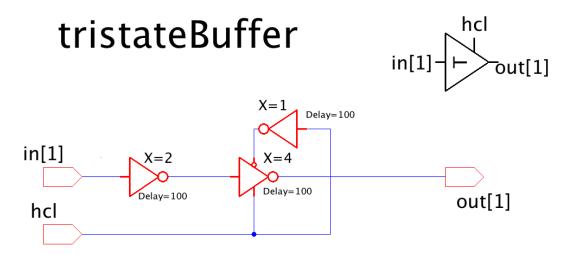

There are two implementation differences between traditional and Telescope GasP. For one, traditional GasP modules have storage, i.e., they control latches in the datapath, where Telescope GasP modules avoid data storage. For instance, signal *cl* in the traditional 6-4 GasP implementation of the Store module in Figure 2.2.1 will clock local latches in the datapath in order to capture and hold data. There is no matching *cl* signal in the Telescope GasP implementation of the Amplify module in Figure 2.2.3.

As a side remark, we can, of course, keep Store signal *cl* in Figure 2.2.1 internal. If we refrain from connecting signal *cl* to any latches in the datapath, the 6-4 GasP implementation becomes storage-free. Internalizing signal *cl* is one possible approach for implementing storage-free modules using traditional GasP. So, the fact that the module does or doesn't have storage control is not unique to Telescope GasP. What's unique is the way control-data bundling relations are maintained, which we'll discuss next.

The second and more crucial difference between traditional and Telescope GasP implementation concerns the communication relation between the input and output channels. In traditional GasP, reverse handshakes on the input channels reset while forward handshakes on the output channels start. This leads to maximum concurrency and produces the low cycle times, low latency, and high throughput that are the hallmarks of GasP [55, 23]. This concurrency is clearly visible in the SPICE simulation in Figure 2.2.2.

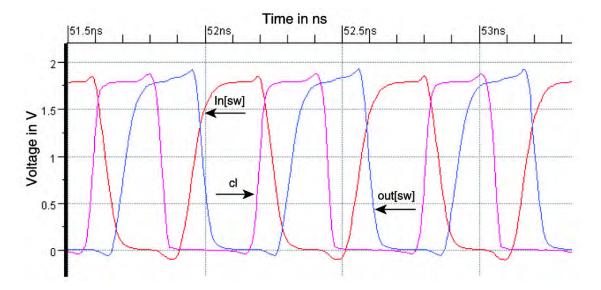

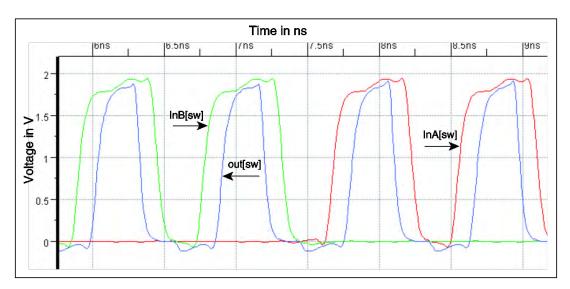

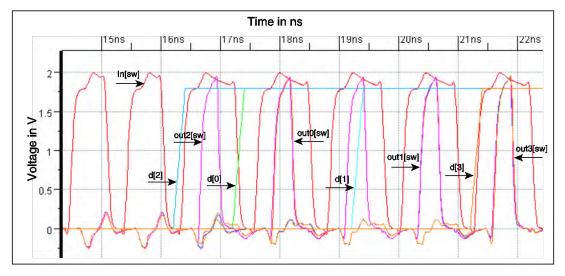

**Fig. 2.2.1:** Circuit for traditional 6-4 GasP module Store, with input handshake signal and master clear *in[sw,mc]*, output handshake signal and master clear *out[sw,mc]*, and local clock signal *cl* to clock data latches for storing data. We use the top-right icon to represent this GasP Store module.

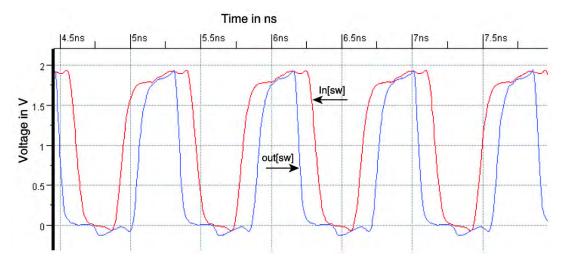

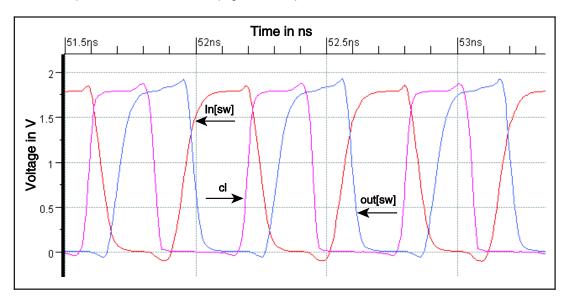

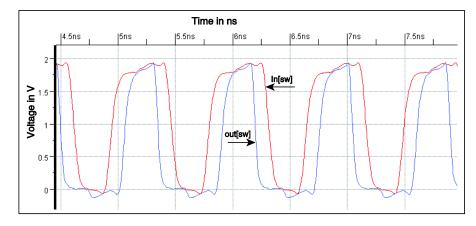

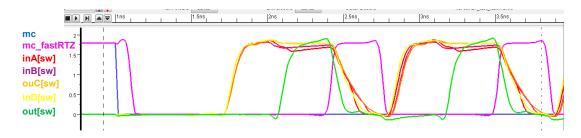

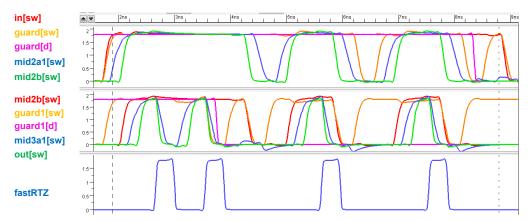

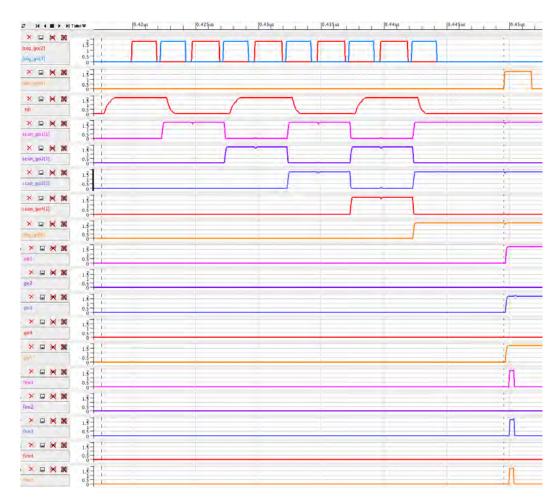

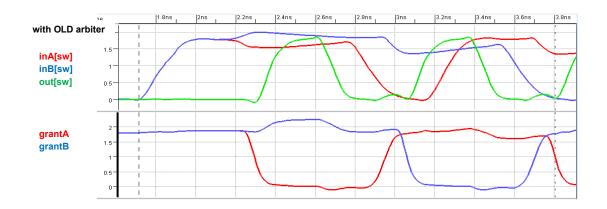

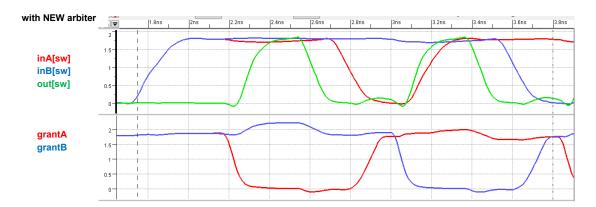

**Fig. 2.2.2:** SPICE-level simulation of the 6-4 GasP implementation of the Store module in Figure 2.2.1. Red signal in[sw] and blue signal out[sw] swap their states in parallel and create a high pulse on clock signal cl, whenever in[sw] is high and out[sw] is low. After in[sw] has gone low, the predecessor in the simulation test environment switches in[sw] back to high. Likewise, after out[sw] has gone high, the successor in the simulation test environment switches out[sw] back to low. Then, the cycle starts again.

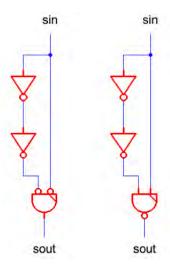

**Fig. 2.2.3:** Circuit for Telescope GasP module Amplify, with input handshake signal and master clear *in[sw,mc]* and output handshake signal and master clear *out[sw,mc]*. We can use either of the two top-right icons to represent this GasP Amplify module.

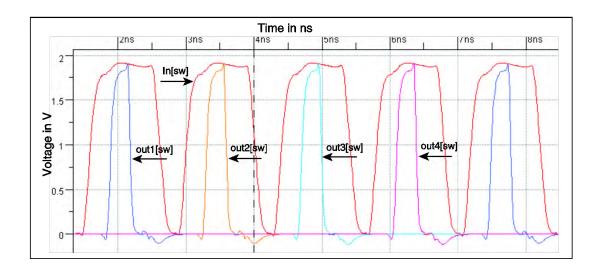

**Fig. 2.2.4:** SPICE-level simulation of the Telescope GasP Amplify module in Figure 2.2.3. Red signal *in[sw]* and blue signal *out[sw]* have a telescopic handshake relationship: *in[sw]* high causes *out[sw]* to go high, and when *out[sw]* has gone low, only then will *in[sw]* go low. The simulation clearly shows that each high pulse on *out[sw]* is strictly contained within a high pulse on *in[sw]*: the blue signal is always below the red signal.

In Figure 2.2.2, the red input handshake signal *in[sw]* resets, i.e., goes low, at the same time that the blue output handshake signal *out[sw]* starts, i.e., goes high. In Telescope GasP, reverse handshakes on the input channels postpone their reset phase until forward handshakes on the output channels have finished both their start and reset phases. This is clearly visible in the SPICE simulation in Figure 2.2.4: each high pulse on the red input signal *in[sw]* completely encapsulates the high pulse on the blue output signal *out[sw]*.

## 2.3 Cost of and Alternatives to Telescope GasP

Because each reverse handshake in the dataflow graph postpones its reset phase until the forward handshake is complete, the control-data bundling constraints in Telescope GasP keep their simple form: a high request signal indicates that the data signals have arrived and that the data values are valid and stable. The strictness with which this simple control-data bundling is maintained may be overkill, but it does avoid the need for latching and it avoids the need for keeping intermediate data outside of Store modules. The price for this simplicity, in particular in combination with single-track handshaking, is extra latency on the reverse path. We will explain this below.

Single-track handshake protocols share state. To separate forward from reverse state in a single-track statewire and create different forward and reverse operations during a single-track handshake, one must add at least one gate inversion in each handshake direction. In the case of non-inverting statewires that use the same encoding, e.g., high for *valid data* and low for *no-longer-valid or irrelevant data*, one must add an even number of inversions in each handshake direction. So, for Telescope GasP, it takes at least four inverter delays per handshake cycle to do something different in the forward direction in comparison to the backward, i.e., reverse, direction. One has only to look at the handshake protocol to realize that forward and reverse functionality are always different

in Telescope GasP: reverse resets wait until forward resets are done. As a result, each Telescope GasP module adds at least four gate delays to the overall cycle time, just to implement telescoping.<sup>1</sup> A pipeline with 6-4 GasP implementations for the Store module and with Telescope GasP implementations for other modules has a minimum cumulative cycle time of 10+4k gate delays, where k is the maximum number of consecutive Telescope GasP modules between Store modules.

This unavoidable increase in cycle time for inserting single-track style repeater modules may be a disadvantage over design styles that work with multi-track handshake signaling and insert multi-track repeater modules. With separate tracks in each forward and reverse handshake direction, it is possible to add gate delays in one direction but not in the other. See for instance the double-track Click circuit in Figure 3.2.2(top), which has gates in the reverse direction but not in the forward direction. Click uses two-phase handshaking over separate tracks [43]. Consequently, Click datapath designs may not experience as much increased cycle time when they use telescoping as do designs with GasP and TGasP. But even in Click, changes in cycle time will be cumulative for pipelines of telescope modules, because of the telescope unfolding and folding sequence.

Should we conclude that the behavioral implications of telescope handshaking combine adversely with the physical implications of single-track handshaking? If so, then perhaps we should avoid using Telescope GasP and instead continue using traditional 6-4 GasP with its minimum constant cycle time of 10 gate delays. Using traditional GasP to implement the dataflow design in Figure 2.1.1 may work if we use additional synchronization between the Store modules at the beginning and end of each datapath. The purpose of such begin-end synchronization is to keep the data latches that feed the combinational logic valid and stable until the latches fed by the combinational logic have captured the computed results. This could provide an alternative solution for using a telescope com-

<sup>&</sup>lt;sup>1</sup>We size transistors using a logical effort model and thus each gate contributes to a unit gate delay.

munication protocol when the goal is to avoid intermediate data storage. It would be a dubious solution when the goal is to bridge long distances. Also, this alternative solution would change the dataflow graph input to ARCwelder, because the dataflow graph would contain extra channel connections and it would use a different handshake signaling sequence. As such, this alternative solution approach is of little help when it comes to mapping *existing* dataflow designs in ARCwelder.

I pursue Telescope GasP for a simple reason: to have a "drop-in," i.e., module-by-module, GasP-style replacement for the dataflow designs already present in ARCwelder and implemented currently using Click Store modules and "Telescope Click" non-Store modules. Assuming that we can make the forward latency in Telescope GasP match the delay needs for control-data bundling, e.g., assuming that the forward latency in the control path matches the delay of the combinational logic, then the art of reducing the datapath cycle time is really in reducing the reverse latency. We can reduce the reverse latency in a datapath by using a fast reset strategy on the reverse handshakes. Section 2.4 contains an example of how this can be done for the Amplify module. The design solutions presented in Appendices A, B, and C show how one can do this for other existing ARCwelder modules that use telescope handshakes.

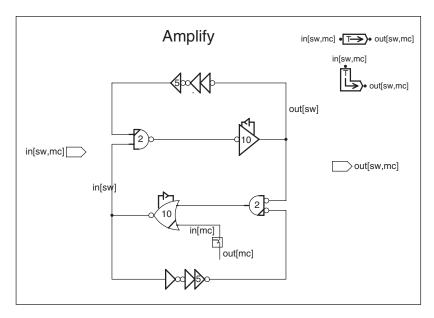

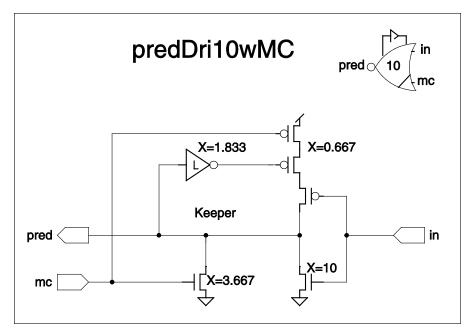

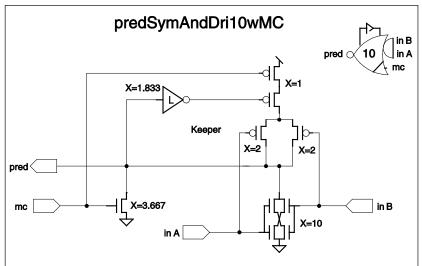

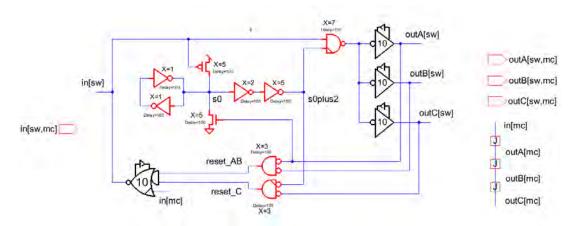

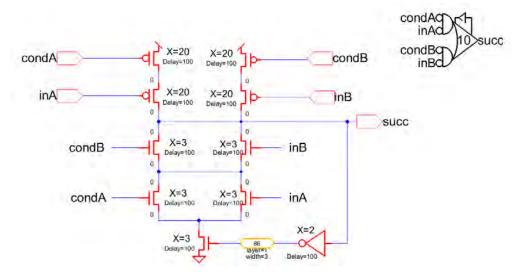

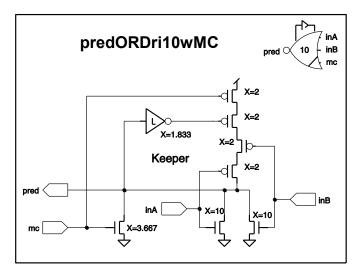

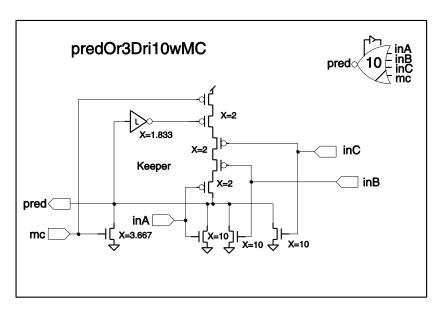

## 2.4 Designing Telescope GasP Modules

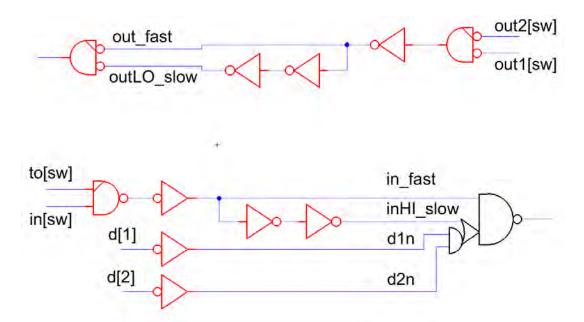

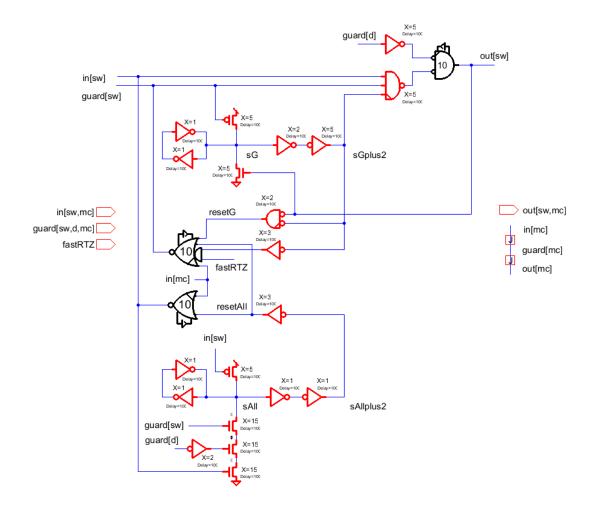

Our actual designs of the Telescope GasP modules can be found in Appendices A, B, and C. Here, in this section, we give only a flavor of the design approach. We explored three different approaches in designing Telescope GasP modules. The first approach uses separate self-resetting loops for input and output channels. The Amplify module in Figure 2.2.3 is an example of this first design approach. It has two self-resetting loops: the loop at the top is used to start and stop the high drive for *out[sw]*, while the loop

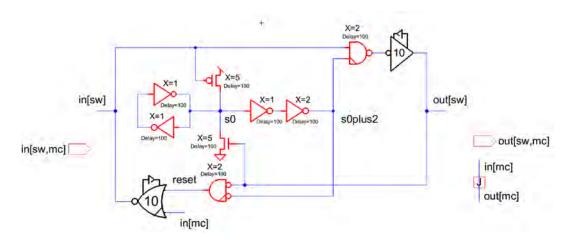

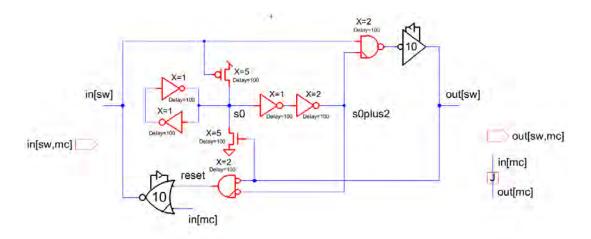

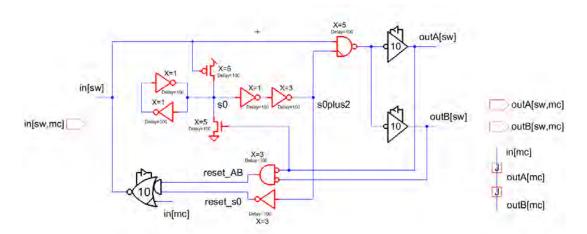

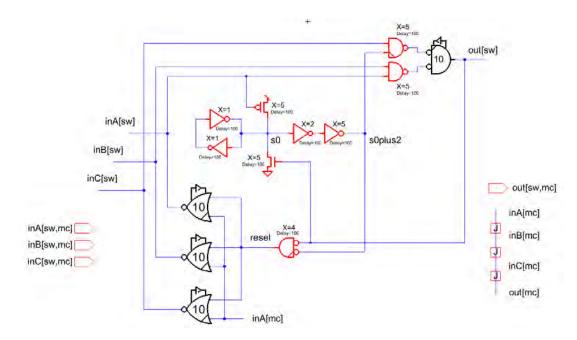

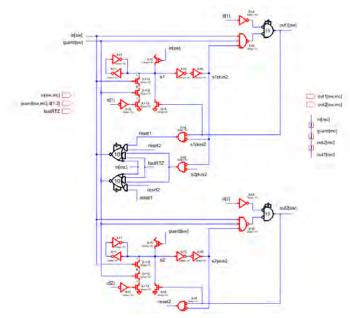

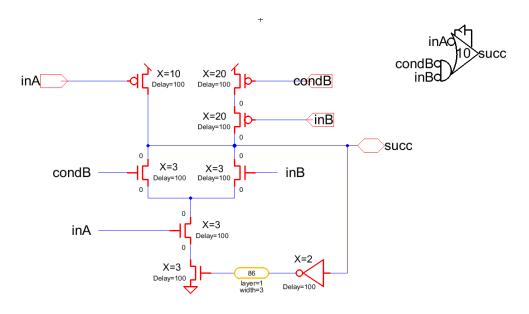

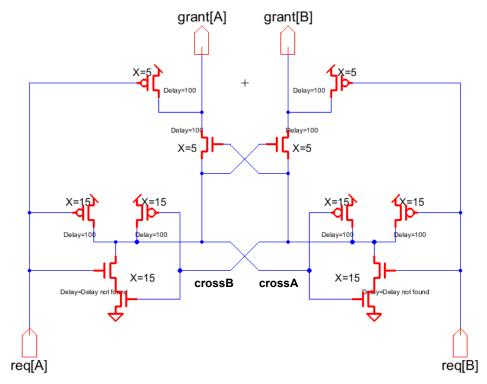

at the bottom is used to start and stop the low drive for *in[sw]*. The second approach shown in Figure 2.4.1 shares the self-resetting loops. It has one self-resetting loop, with separate taps to start and stop the high respectively low drives for *out[sw]* and *in[sw]*. The second design approach is based on the repeater design by Jo Ebergen et al. [10] but we generalized the approach to other modules beyond Amplify. The third design approach shown in Figure 2.4.2 uses separate self-resetting loops for handshake signals as used in the first design, but it cross-couples the loops to improve timing margins. This is explained in more detail further on.

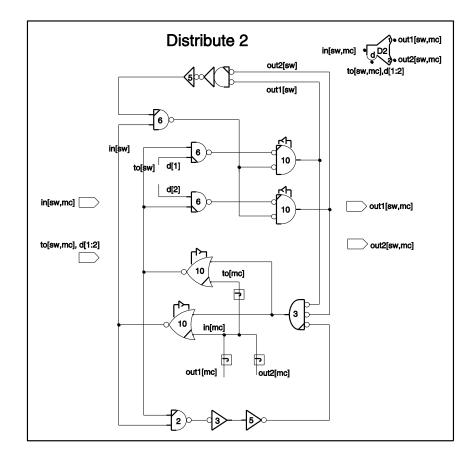

All three approaches have their advantages and disadvantages. The advantage of the first approach used in Figure 2.2.3 is that its control-data bundling constraints are less strict than those for the second approach used in Figure 2.4.1. This is not immediately obvious from the Amplify design, but it will become obvious when we get to the data-controlled Distribute modules. For details, see Appendix B.

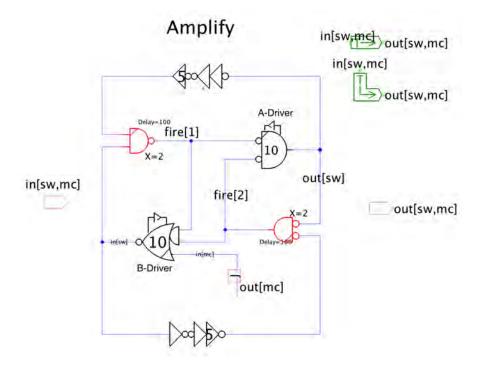

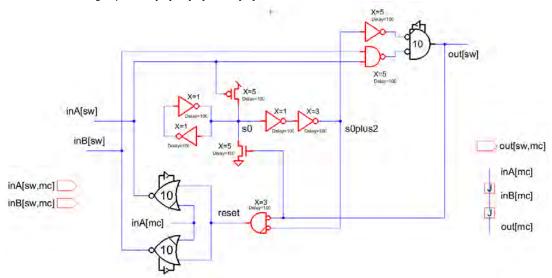

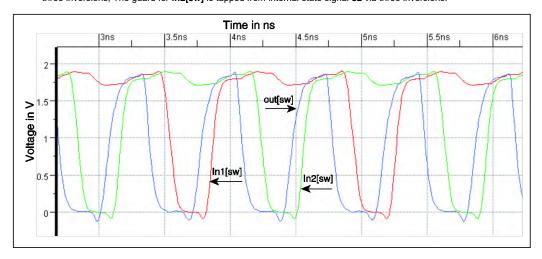

The advantage of the second approach used in Figure 2.4.1 is that it has timing margins that we feel are safe — safer than those in the first approach. The caption of Figure 2.4.3 contains a detailed explanation of the Amplify operation and safe timing margins in the second design approach.

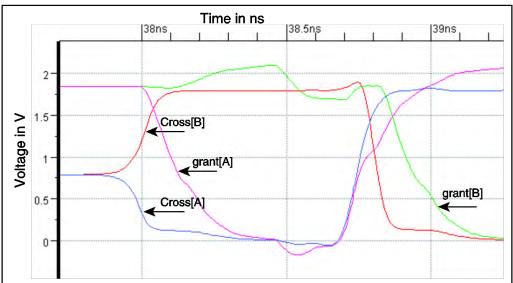

In contrast to the safe timing margins in the second design approach, the first design approach in Figure 2.2.3 has two marginal relative timing constraints:

1. After in[sw] rises, it takes 2 gate delays before out[sw] rises and disables the inverted input AND gate in the lower self-resetting loop, while it takes 3 gate delays for the high in[sw] signal to enable that same AND gate via the lower self-resetting loop. To guarantee a telescope relation between in[sw] and out[sw], the inverted input AND gate must sense the disabling out[sw] transition before it senses the enabling in[sw] transition. The timing margin between the two is only 1 gate delay.

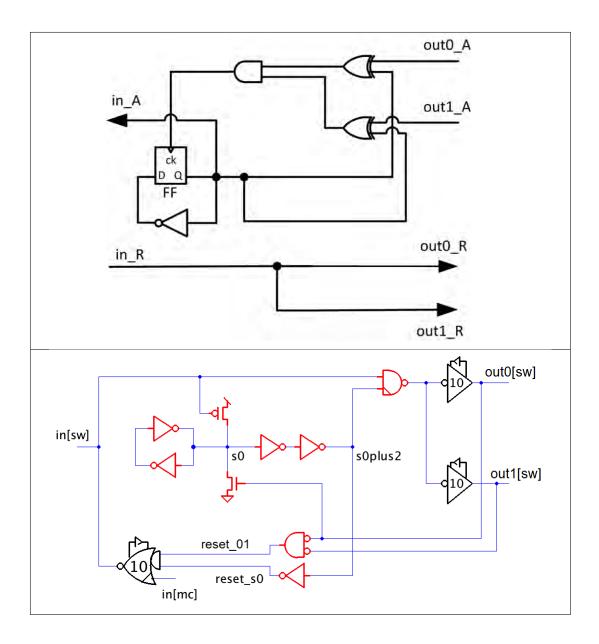

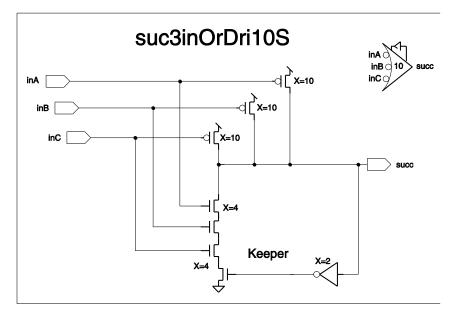

**Fig. 2.4.1:** Our second alternative Telescope GasP circuit implementation for module Amplify. It differs from the first one in Figure 2.2.3, because it shares the self-resetting loops between the input and output handshakes insofar possible.

**Fig. 2.4.2:** Our third alternative Telescope GasP circuit implementation for module Amplify, similar to the first one in Figure 2.2.3 but with better timing margins.

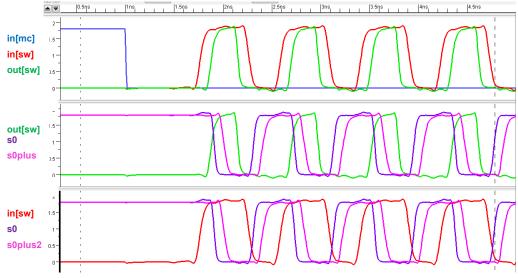

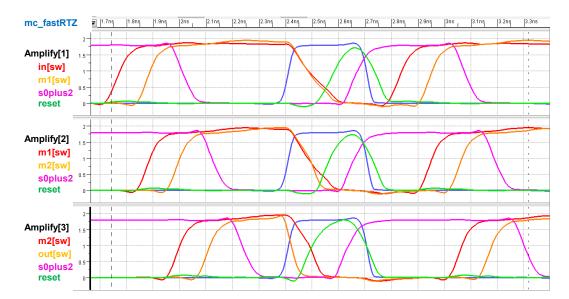

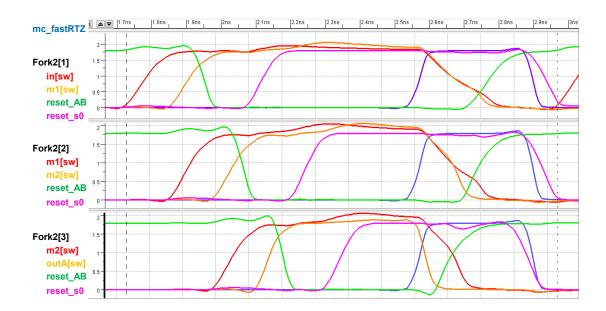

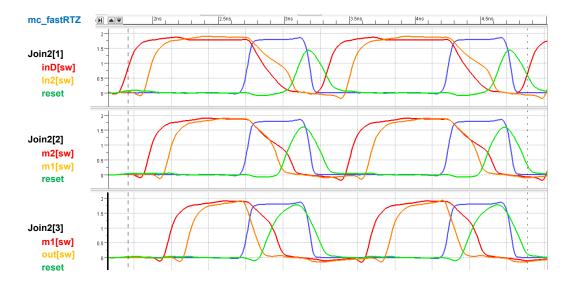

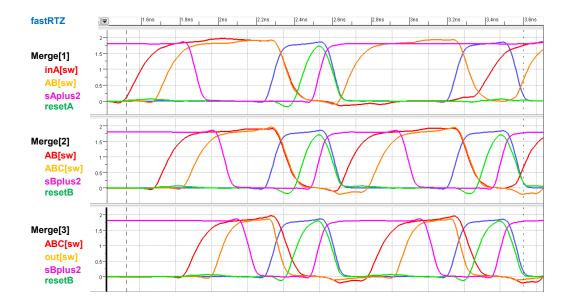

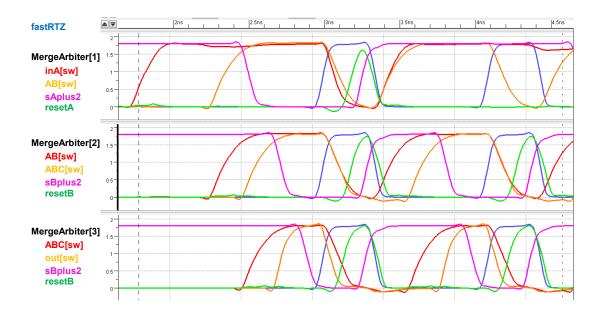

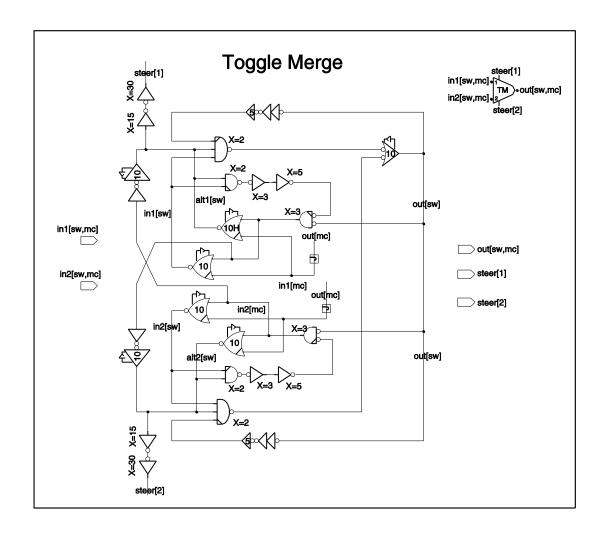

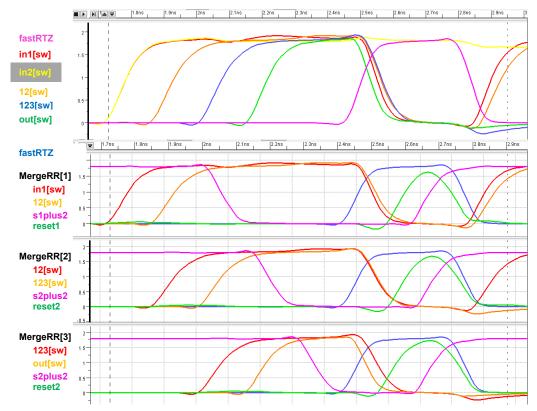

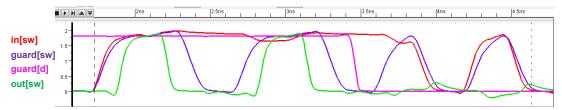

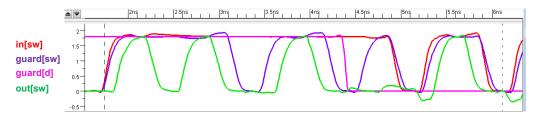

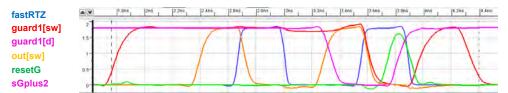

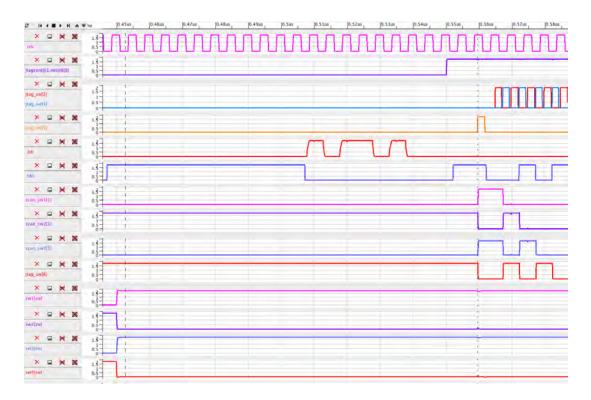

Fig. 2.4.3: SPICE-level simulation of module Amplify in Figure 2.4.1.

- The top window shows the telescopic handshake relation between in[sw] and out[sw].

- The middle window shows the simulated timing margins from <code>out[sw]</code> high to s0 low (1 gate delay) and to s0plus2 low (3 gate delays) and to stopping the high drive on <code>out[sw]</code> (5 gate delays). The <code>in[sw]</code> reset timing margin of 3 gate delays that we see when going from <code>out[sw]</code> high, disabling the inverted input AND gate, to s0plus2 low, enabling the AND gate, is large enough to guarantee the telescopic relation between <code>in[sw]</code> and <code>out[sw]</code>. It is also small enough to fit within the high pulse width of 5 gate delays for <code>out[sw]</code> in order to maintain throughput. The remaining 2 gate delays after s0plus2 goes low are used to stop the high drive on <code>out[sw]</code> so the receiver can reset <code>out[sw]</code> without a fight conflict.

- Similar to the middle window, the bottom window shows the simulated delay margins from in[sw] going low to s0 high (1 gate delay) and to s0plus2 high (3 gate delays) and to stopping the low drive on in[sw] (5 gate delays). The out[sw] set timing margin of 3 gate delays that we see when going from in[sw] low, disabling the NAND gate, to s0plus2 high, enabling the NAND gate, is large enough to guarantee a telescopic handshake relation between in[sw] and out[sw]. It is also small enough to fit within the low pulse width of 5 gate delays for in[sw] in order to maintain throughput. The remaining 2 gate delays after s0plus2 goes high are used to stop the low drive on in[sw], so the sender can set in[sw] without a fight conflict.

**Fig. 2.4.4:** Delay circuits to increase the timing margin from *sin* low to *sout* high by two gate delays (left), and to increase the delay from *sin* high to *sout* low by two gate delays (right). Other path delays remain unchanged.

2. After out[sw] falls, it takes 2 gate delays before in[sw] falls and disables the NAND gate in the upper self-resetting loop, while it takes 3 gate delays for the low out[sw] signal to enable that same NAND gate via the upper self-resetting loop. To guarantee a correct handshake relation between in[sw] and out[sw], the NAND gate must sense the disabling in[sw] before it senses the enabling out[sw] transition. The timing margin between the two is only 1 gate delay.

A timing margin of only 1 gate delay is marginal and sensitive to noise interference and process variations. We can make both margins as safe as the timing margins deployed in the second approach by adding extra circuitry to delay the transition that must arrive later by two additional gate delays. Other transitions remain unaffected. For instance, to delay a transition from *sin* low to *sout* high we insert the left-hand circuit of Figure 2.4.4, and to delay a transition from *sin* high to *sout* low we insert the right-hand circuit of Figure 2.4.4.

The two delay circuits in Figure 2.4.4 add two gate delays to the targeted *sin*-to-*sout* transition. Depending on the actual cycle time of the module in the given datapath, we can extend this further to four additional gate delays or more, without losing throughput.

These two types of delay circuits are sufficiently generic for our needs, and have the following properties:

- The target transition is slowed down by sufficient margin.

- The target transition is fast enough to sustain maximum throughput.

- The delays of the other transitions remain unchanged.

Adding delay circuits to improve the timing margin has one limitation. The delay circuits are asymmetric in nature, which limits the maximum gate delays one can obtain by inserting such delay modules. In this thesis, the maximum number of gate delays is 5, as limited by the 5-gate delay pulse width of 6-4 GasP.

An alternative to adding delay circuits in the first design is to use the third design approach shown in Figure 2.4.2, which has the following relative timing constraints:

- 1. After in[sw] rises, it takes 1 gate delay to disable the B-Driver gate in the lower self-resetting loop, while it takes 4 gate delays for the high in[sw] signal to enable this B-Driver gate via the lower self-resetting loop. To guarantee a telescope relation between in[sw] and out[sw], the B-Driver gate must sense the in[sw]-based disabling transition before it senses the in[sw]-based enabling transition. The timing margin between the two is 3 gate delays, which we consider safe.

- 2. After out[sw] falls, it takes 1 gate delay to disable the A-Driver in the upper self-resetting loop, while it takes 4 gate delays for the low out[sw] signal to enable the same A-Driver via the upper self-resetting loop. To guarantee a correct handshake relation between in[sw] and out[sw], the A-Driver gate must sense the out[sw]-based disabling transition before it senses the out[sw]-based enabling transition. The timing margin between the two is 3 gate delays, which we consider safe.

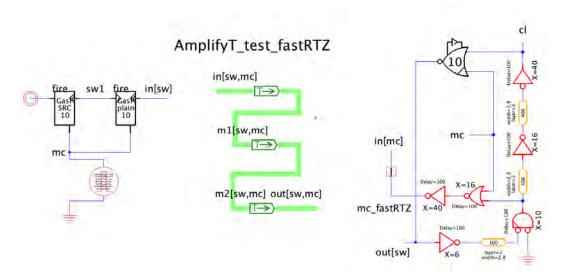

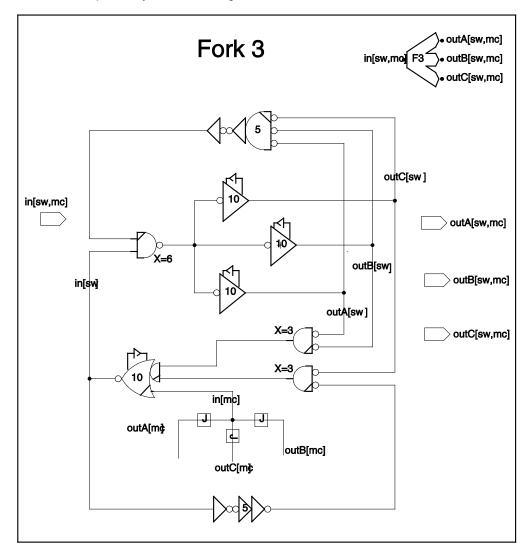

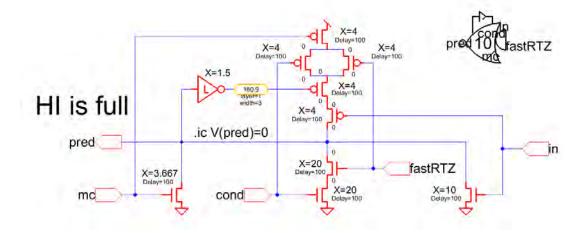

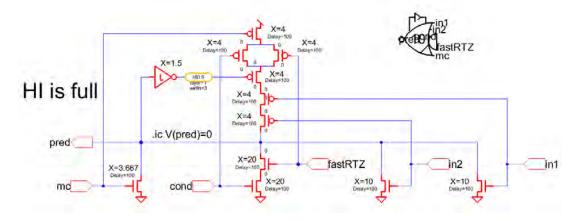

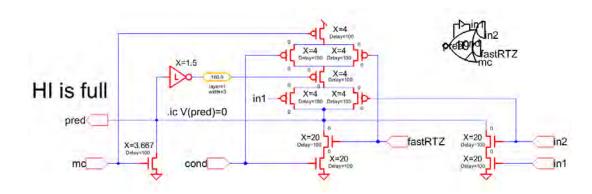

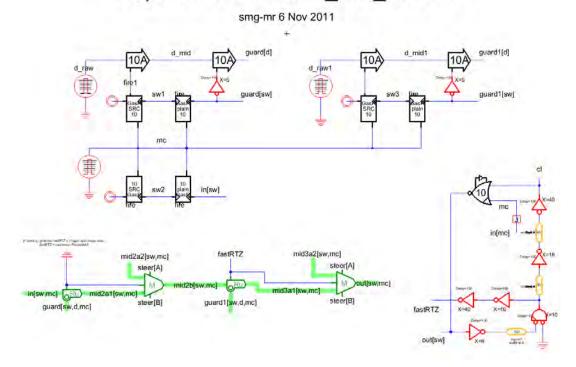

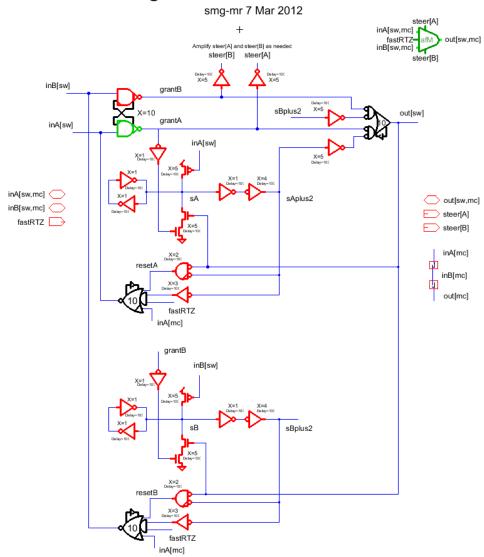

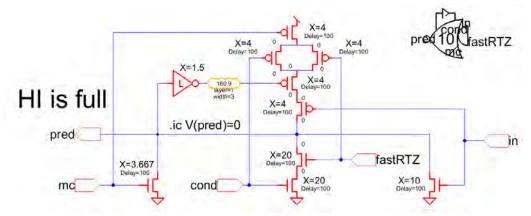

**Fig. 2.5.1:** Fast reset configuration to reset concurrently the three Amplify modules in the middle First In First Out (FIFO) design.

The key advantage of the third design approach in Figure 2.4.2 is that both relative timing constraints have a safe timing margin of 3 gate delays. A disadvantage of the third design approach is that the complexity of the A-Driver and B-Driver gates increases as each gate gets an additional input.

### 2.5 Latency Reduction in the Reverse Direction

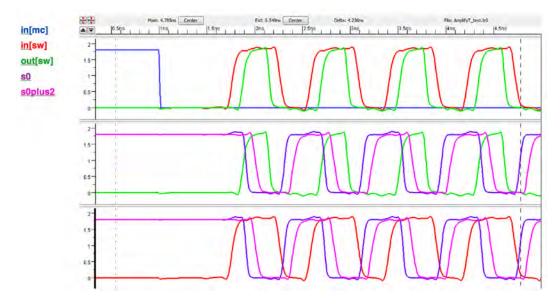

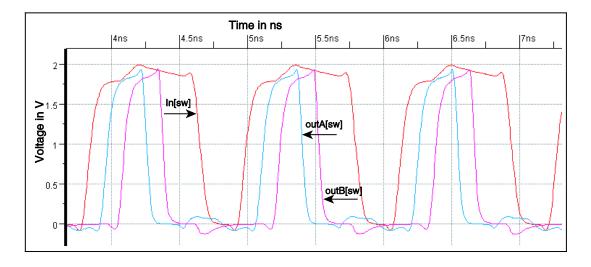

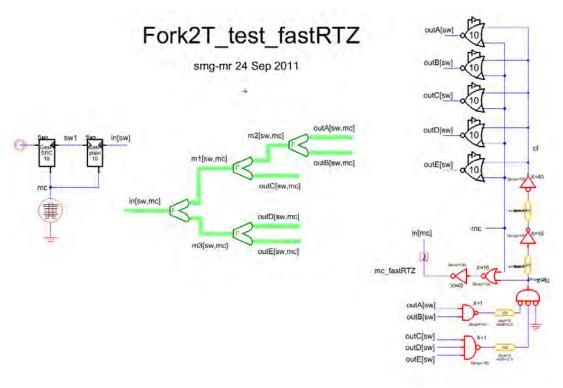

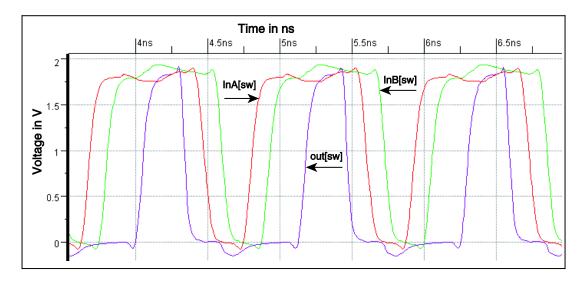

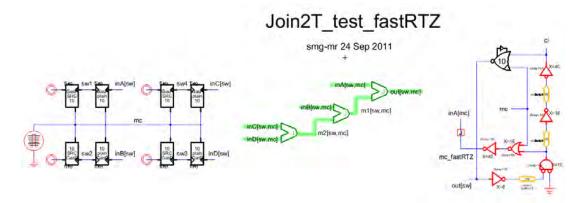

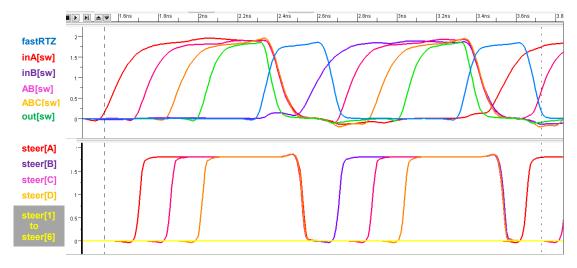

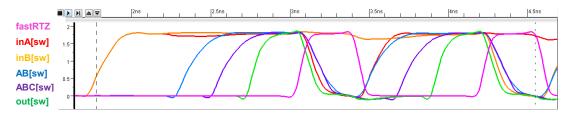

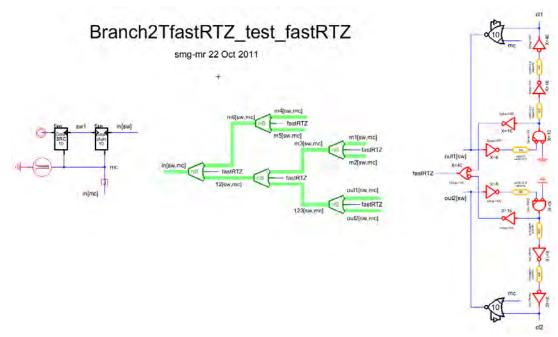

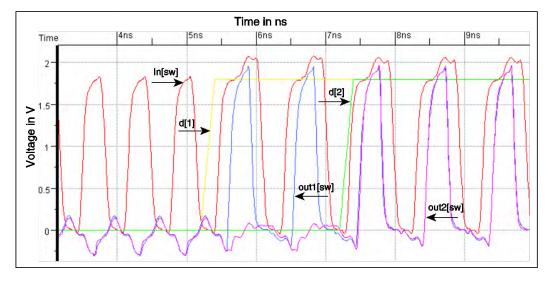

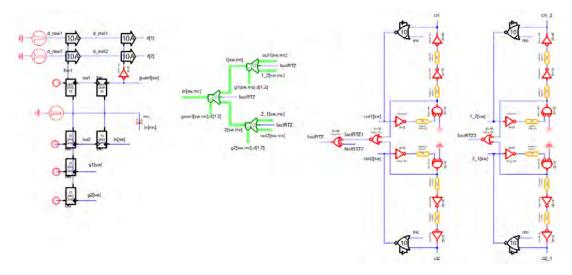

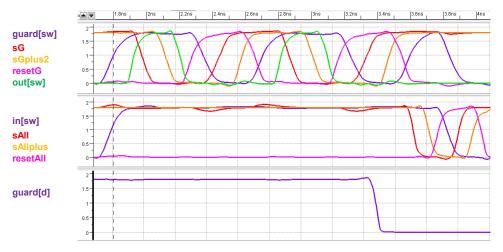

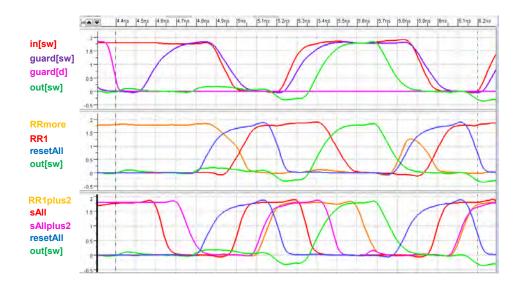

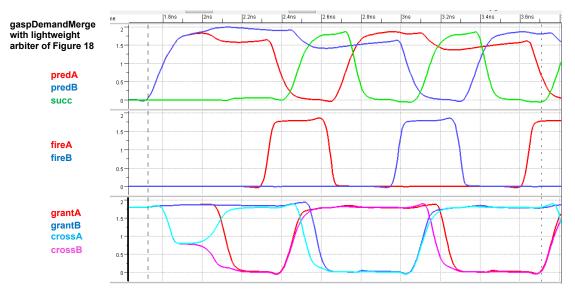

In addition to the single module test configuration used for Figure 2.4.3, we also tested the behavior of the Amplify module in a datapath configuration consisting of a First In First Out (FIFO) configuration of Amplify modules. The purpose of this second test configuration was to show how one could generate a fast reset signal to shorten the reverse latency in the datapath. This second test configuration follows in Figure 2.5.1.

Figure 2.5.1 shows a sender FIFO configuration on the left, designed using traditional 6-4 GasP modules. The sender FIFO feeds a datapath consisting of another FIFO con-

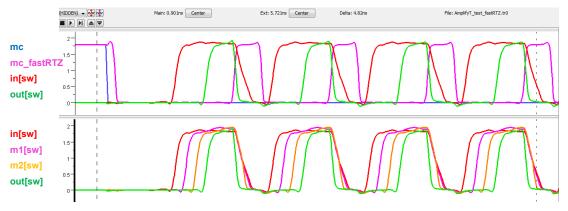

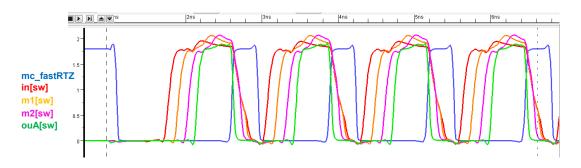

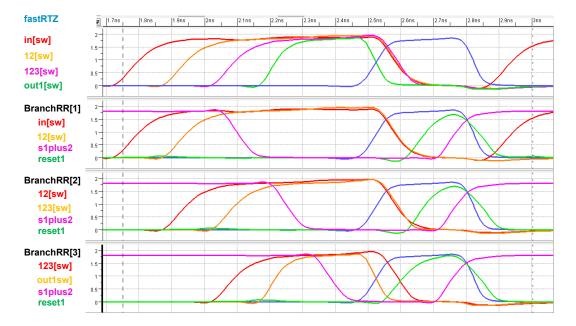

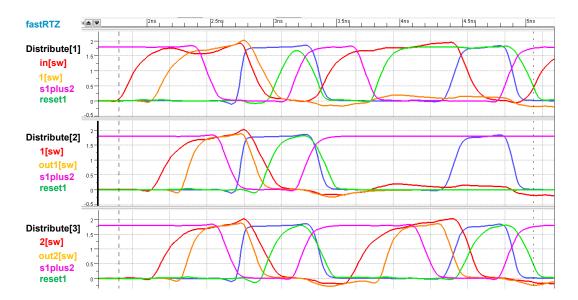

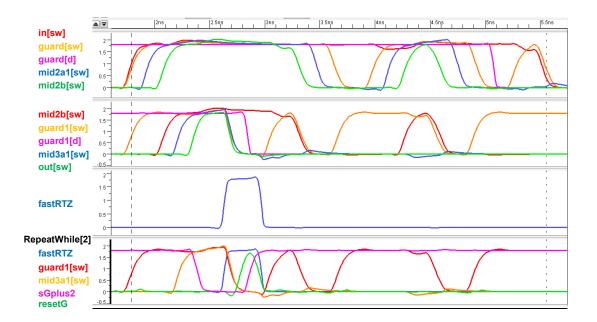

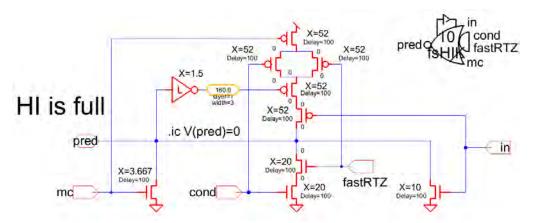

Fig. 2.5.2: Fast reset SPICE-level simulation results for the test configuration in Figure 2.5.1.

- The top window shows how the pink high pulse on the fast reset signal,  $mc\_fastRTZ$ , resets concurrently both the green handshake on out[sw] of the third Amplify module and the red handshake on in[sw]. The reset slope for out[sw] is steeper than the reset slope for in[sw] because: (1) out[sw] is reset first by  $mc\_fastRTZ$  and two gate delays later also by out[sw] via the negated input AND gate in the third Amplify module and the strong cl-to-out[sw] driver in the Store module, while (2) in[sw] is reset first by  $mc\_fastRTZ$ , and two gate delays later by a weaker driven m1[sw].

- The bottom window shows the beginning and end of each handshake over the initial, intermediate and final statewires in[sw], m1[sw], m2[sw], and out[sw] in the Amplify queue. The handshakes at the output channel of each module start 2 gate delays after the handshakes at the input channel. But thanks to the fast reset signal,  $mc\_fastRTZ$ , shown in the top window, all outstanding handshakes end at the same time. The steepness of the reset slopes for in[sw], m1[sw], m2[sw], out[sw] depends on how many modules there are between the statewire and the Store module at the end of the datapath: the fewer modules in-between, the steeper the slope. This is because the second drive wave for resetting each handshake comes from the successor module, which is strongest when coming from the Store module. In the above text for the top window, we already explained the slope differences for the falling transitions on in[sw] versus out[sw]. The bottom simulation window clearly shows that differences in slope peter out quickly: the slope differences for the falling transitions on in[sw], m1[sw], and m2[sw] are significantly less prominent.

figuration with three Amplify modules, designed in Telescope GasP using the circuit implementation of Figure 2.4.1. The right-hand side shows the receiving half of a Store module, designed in 6-4 GasP using the implementation of Figure 2.2.1. We deleted the sending half from this Store module because we don't need it, and we added extra circuitry to generate a fast reset signal, called *mc fastRTZ*.

When the input handshake signal to the Store module on the right rises, i.e., out[sw] goes high, the module generates a 5-gate-delay high pulse on  $mc\_fastRTZ$ , which is distributed to reset concurrently all outstanding handshakes for the Amplify modules in the middle FIFO. This works, as can be seen from the SPICE simulation in Figure 2.5.2. The cycle time for the Amplify FIFO without a fast reset signal would be 10 + 3\*4 = 22 gate delays. With the fast reset signal we obtain a cycle time of 10 + 3\*2 = 16 gate delays. These results are same with the Amplify implementations of Figures 2.2.3 and 2.4.2.

# 2.6 Summary and Conclusions

This chapter introduced Telescope GasP, or TGasP, to have a module-by-module GasP-style replacement for the dataflow designs already present in ARCwelder and implemented currently using Click Store modules and "Telescope Click" non-Store modules. The idea is that, instead of mapping a Store module to a Click Store circuit, ARCwelder can now map a Store module to a GasP Store circuit. And, instead of mapping a non-Store module to a specific "Telescope Click" circuit implementation, ARCwelder can now map a non-Store module to a TGasP circuit implementation. In the next chapter, I will discuss the ARCwelder compiler extensions for GasP and TGasP.

I introduced the term "telescope" for the communication behavior of a "telescope" module, because the forward extension of its communication channels with *valid data* and the

reverse shortening with *no-longer-valid or irrelevant data* are reminiscent of the extension and shortening of a jointed telescope with sliding tubes, as illustrated in Figure 2.1.1.

Telescope handshake modules can be used to avoid intermediate data storage, which is the key reason why Willem Mallon incorporated them in ARCwelder. They can also be used as repeater modules to bridge long distances.

An alternative solution to avoid intermediate storage — over short distances — would be to maintain a parallel communication protocol, such as used by Store modules, and avoid storing intermediate data but to keep the data stable and valid for as long as needed by adding extra — short-distance — synchronization channels between the Store modules at the beginning and end of each datapath.

Telescope GasP suffers from latency in the reverse direction of the dataflow. Section 2.5 and Appendices A, B, and C present a fast reset solution to ameliorate this problem. There are similarities between implementing these fast reset solutions for Telescope GasP and implementing a datapath begin-to-end synchronization scheme for traditional GasP. Further investigations of these similarities are outside the scope of this thesis. Also outside the scope of this thesis are our continued investigations as to where and by how much we might want to change the forward and reverse latencies in Telescope GasP. The low 2-gate-delay latencies used in this thesis result in a myriad of custom driver designs.

# 2.7 My Contributions for Chapter 2

While most of this thesis is joint work with my supervisors, the following key contributions are largely mine.

- I extended the GasP-style circuit family with Telescope GasP (TGasP) modules.

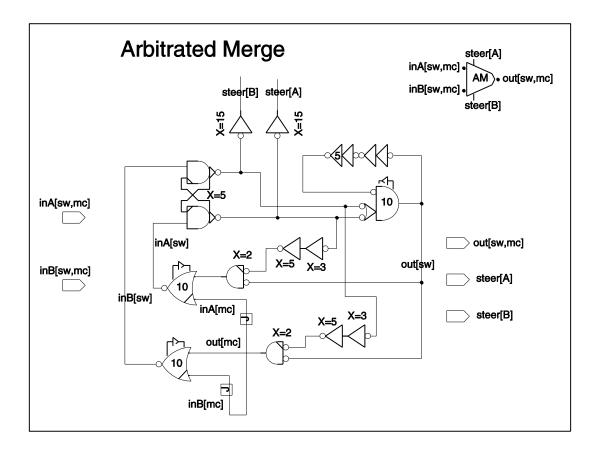

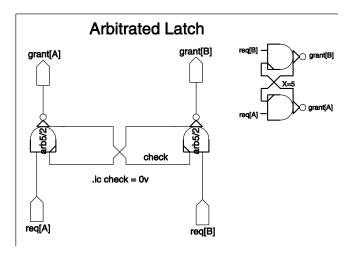

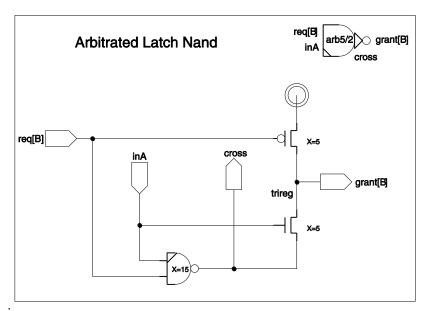

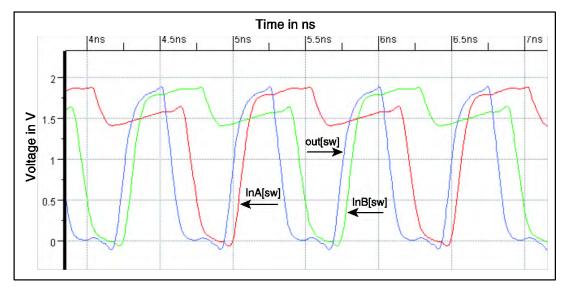

I developed a representative set of TGasP modules for control-driven and data-driven dataflow control operations: fork, join, branch, case selection, non-arbitrated and arbitrated merge, and repetition. The corresponding TGasP module designs follow in the ARC reports in Appendices A, B, and C. All modules have been sized correctly and have been simulated with SPICE to validate their behaviors.

- I developed three different circuit design approaches to implement each Telescope GasP module, and explored their advantages and disadvantages in terms of design complexity and timing.

# Silicon Compilation for Click and GasP

To design any computer system of substance, we need design tools [7][14], preferably a silicon compiler – with a user interface to enter the design at a high enough level so we can focus on algorithmic correctness before we map it to a circuit implementation, and with a suite of analysis tools so we can evaluate the various implementation options in terms of energy, throughput, latency, and area. Few silicon compilers are available that support self-timed design. Some of the best known ones are proprietary, owned by companies like Tiempo [5] and Fulcrum [3].

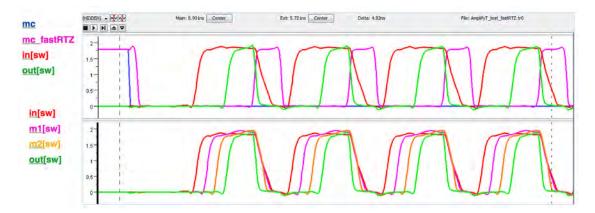

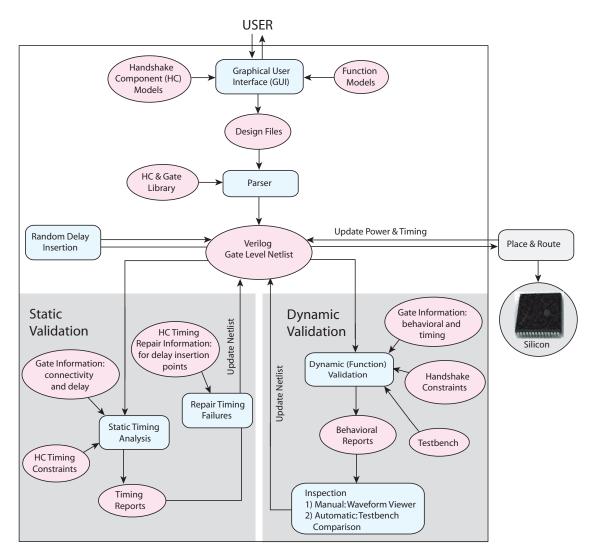

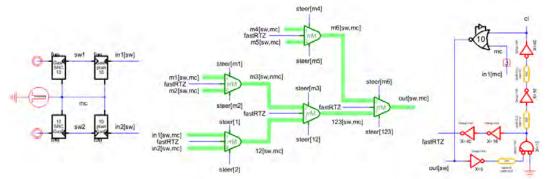

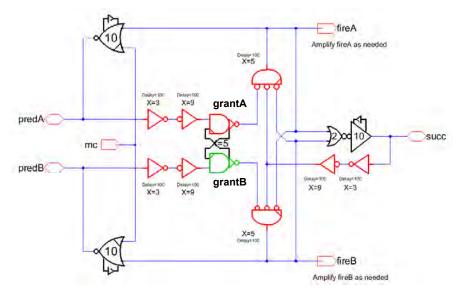

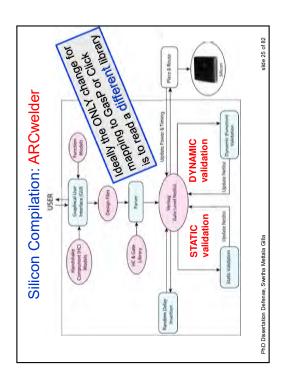

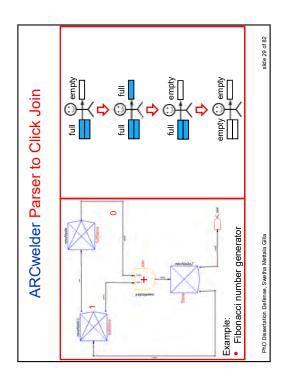

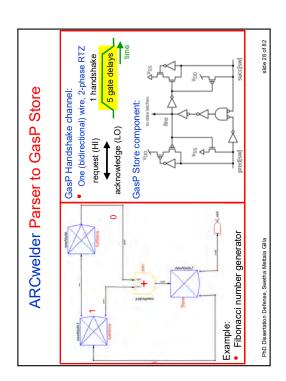

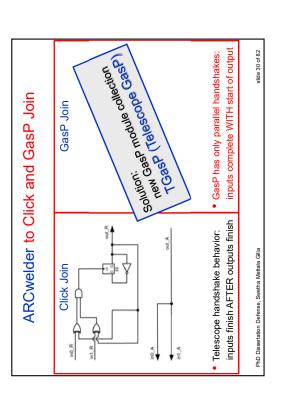

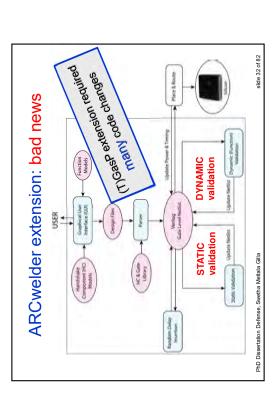

This chapter summarizes the changes made to the ARC's silicon compiler, ARCwelder, so it compiles dataflow designs to both Click and GasP-style implementations.

ARCwelder was developed by Willem Mallon, between 2010 an 2012, when Willem worked at the Asynchronous Research Center (ARC) at Portland State University. The compiler maps dataflow designs to VLSI circuits and – ultimately – to silicon. The name of the compiler reflects how, at the user interface, ARCwelder welds together both text and graphics to convey the intent of the design.

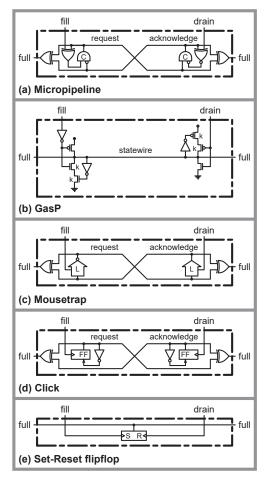

The organization of ARCwelder is based on that of the last compiler developed by Philips Handshake Solutions [43]. The compiler focuses on dataflow designs, as opposed to the control-oriented focus of previous compiler generations developed and supported by Handshake Solutions and the prior Philips Tangram team [42, 60]. The reason for this focus shift was caused by a shift in applications requested by the customers of Handshake Solutions. Originally, most applications were in the area of low power, automotive, smart cards, and distributed control. But more and more customers were seeking higher throughput applications in the signal-processing domain. After delivering the asynchronous ARM996HS in 1996, which was licensed through ARM Ltd, the design engineers at Handshake Solutions realized that this type of design stretched the compiler capabilities to the limit in terms of circuit latency and throughput. Meanwhile, the test engineers had come to the conclusion that, despite intense collaboration between Handshake Solutions and the Computer Aided Design (CAD) tool companies they worked with, the CAD tools were largely incapable of dealing with latch-based designs. As a result, most of the latches had to be replaced by flipflops to permit static timing analysis, fault simulation, and test generation. The engineers developed a new circuit family, called Click, which uses flipflops instead of latches. All loops in Click go through flipflops. The data are tightly coupled to the control flow to accommodate pipelined applications with high throughput dataflows while saving power and energy. Click is the most synchronous asynchronous self-timed circuit family we know of. Commercial CAD tools for static timing analysis, fault simulation, and test generation have an easier task dealing with Click circuits than with most other self-timed circuits. For Handshake Solutions, supporting Click required the development of a new compiler [43]. Neither Click nor its compiler were patented, because by that time Philips was closing down Handshake Solutions.

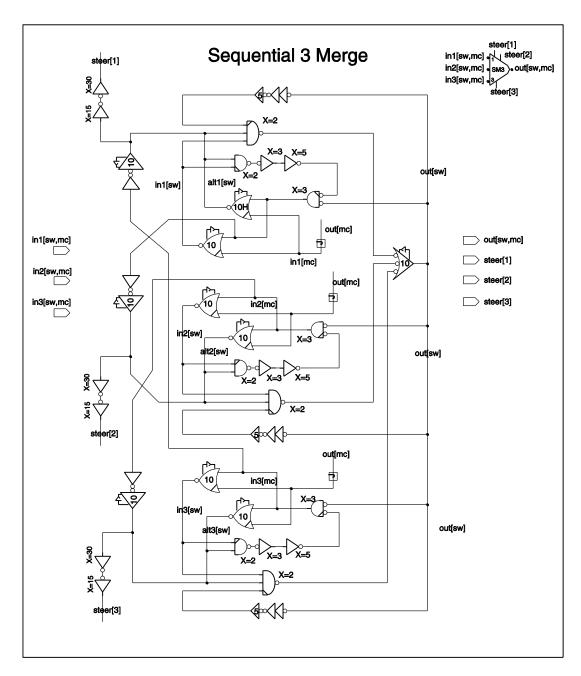

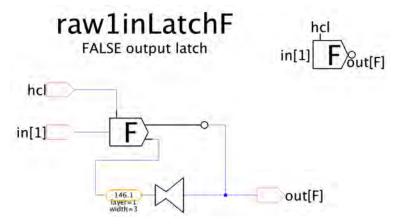

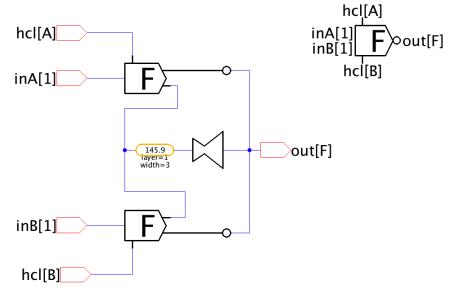

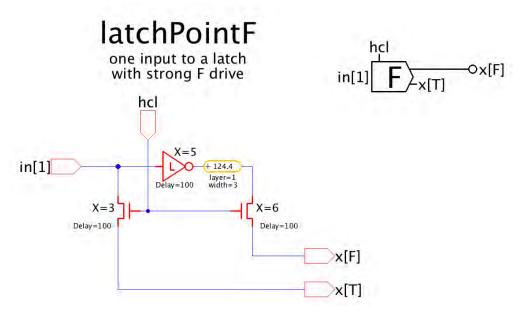

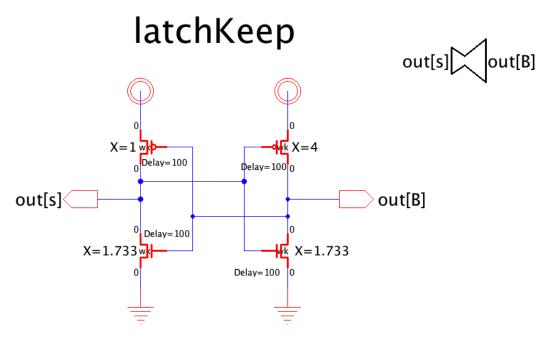

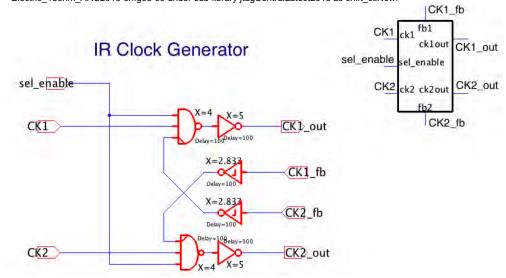

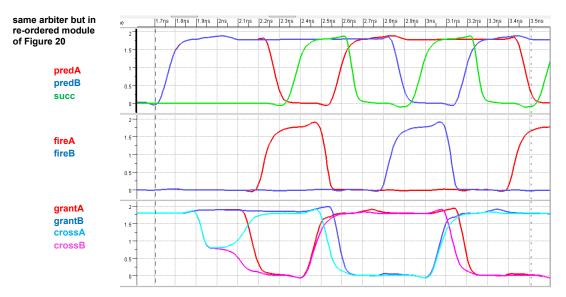

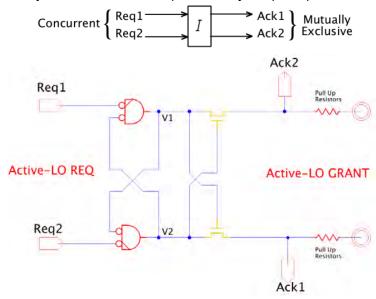

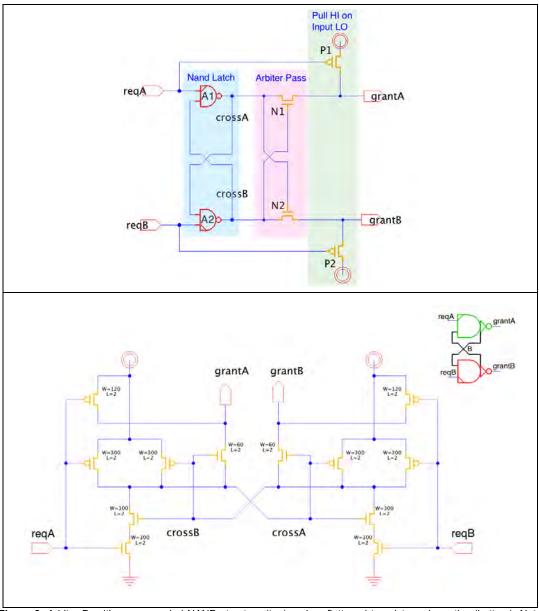

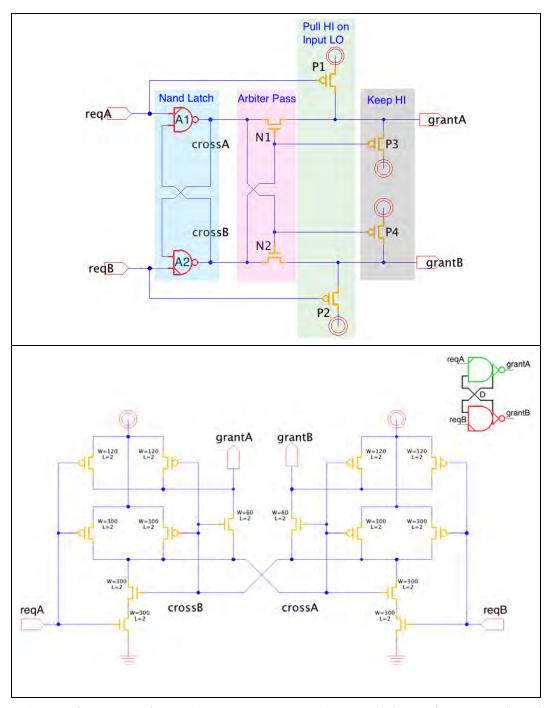

At the ARC, we're trying to save some of the key insights and knowledge built up by Handshake Solutions, starting with Click and its compiler. Willem Mallon has played a key role in kick-starting this effort, and is still dedicated in continuing it through his Dutch