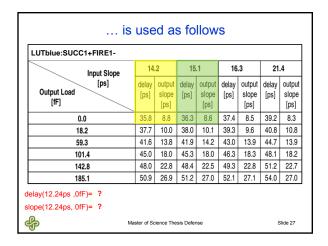

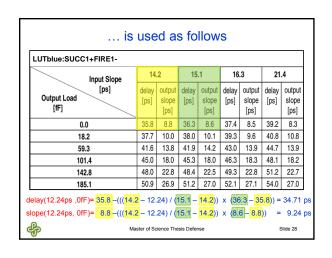

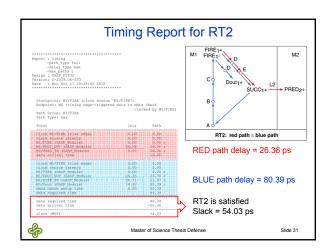

| Input Slope [ps] Output Load [ff] | 14            | 14.2                    |               | 15.1                    |               | 16.3                    |               | 21.4                    |  |

|-----------------------------------|---------------|-------------------------|---------------|-------------------------|---------------|-------------------------|---------------|-------------------------|--|

|                                   | delay<br>[ps] | output<br>slope<br>[ps] | delay<br>[ps] | output<br>slope<br>[ps] | delay<br>[ps] | output<br>slope<br>[ps] | delay<br>[ps] | output<br>slope<br>[ps] |  |

| 0.0                               | 35.8          | 8.8                     | 36.3          | 8.6                     | 37.4          | 8.5                     | 39.2          | 8.3                     |  |

| 18.2                              | 37.7          | 10.0                    | 38.0          | 10.1                    | 39.3          | 9.6                     | 40.8          | 10.8                    |  |

| 59.3                              | 41.6          | 13.8                    | 41.9          | 14.2                    | 43.0          | 13.9                    | 44.7          | 13.9                    |  |

| 101.4                             | 45.0          | 18.0                    | 45.3          | 18.0                    | 46.3          | 18.3                    | 48.1          | 18.2                    |  |

| 142.8                             | 48.0          | 22.8                    | 48.4          | 22.5                    | 49.3          | 22.8                    | 51.2          | 22.7                    |  |

| 185.1                             | 50.9          | 26.9                    | 51.2          | 27.0                    | 52.1          | 27.1                    | 54.0          | 27.0                    |  |

Slide 32

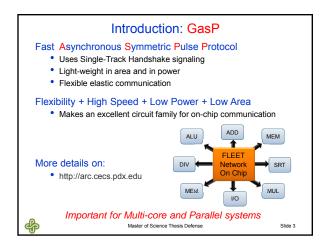

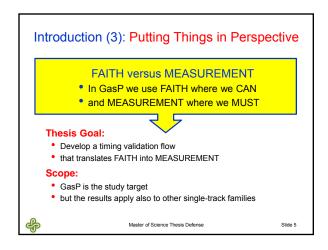

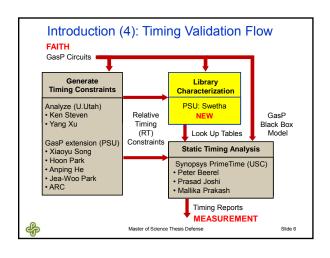

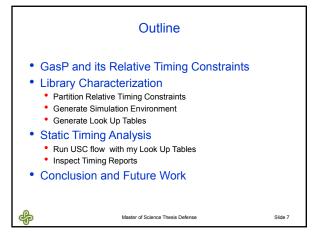

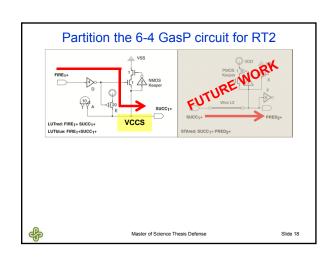

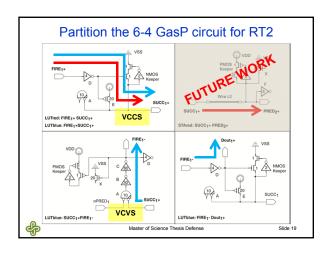

## Conclusion and Future Work Take-Away: • We now have a Timing Validation flow for single-track circuits • It translates FAITH (design assumptions) into MEASUREMENT • by generating Look Up Tables • that go into the USC Static Timing Analysis flow • which reports how well the FAITH holds up • The proof of the pudding is in the eating • I used this flow to validate relative timing assumptions in 6-4 GasP • The results match with the results of my ASYNC 2010 publication Future Work: • Wire delay model • with near-end capacitive load and far-end delay information

Master of Science Thesis Defense

Flow automation