There are multiple reasons for designing asynchronous or self-timed circuits, systems, and algorithms: low power, low energy, low delay-sensitivity, and low electro-magnetic interference, as well as high speed, high delay-tolerance, and high scalability.

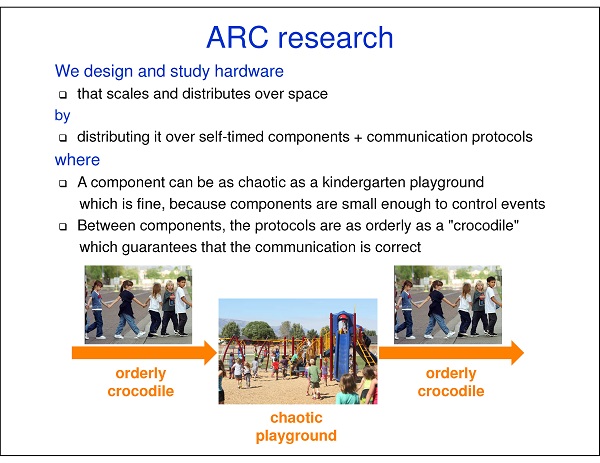

Our goal is to design and study hardware and algorithms that scale and distribute over space and time. We do this by dividing the hardware into self-timed components and communication protocols. Inside our basic non-composite component, behaviors can be as chaotic as a kindergarten playground. This is fine, because basic components are small enough to oversee and control events. The protocols between the components are as orderly as a “crocodile” chain of children going from playground to playground, which guarantees that the communications are correct.

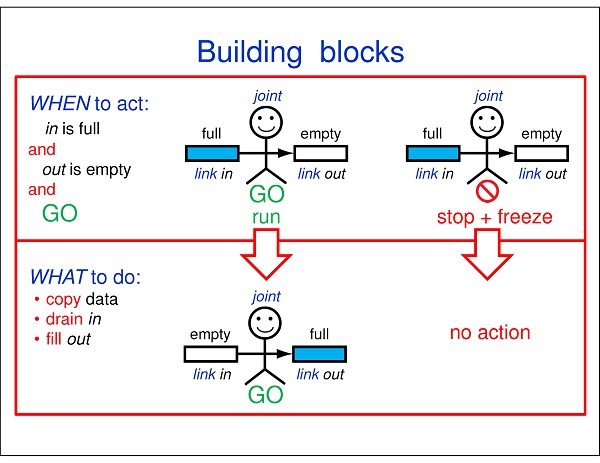

Instead of “crocodile” and “kindergarten” we use the terms Link and Joint. Links transport and store data, while Joints compute and control the flow of data. To emphasize their transport and storage capability, we sometimes draw Links as long rectangles. To emphasize their dataflow manipulation capability, we sometimes draw Joints as stick figures.

Links and Joints interact using a full-empty or turn-based protocol – a generic handshake protocol that follows good conversation practice. In good conversations, one listens while the other speaks. As the conversation progresses, listener and speaker take turns. Following good conversation practice, the Link-Joint protocol lets Joints take turns updating the one-to-one Links connecting them. Each Joint action can be controlled with an individual go signal. The individual go signals enable us to start and stop self-timed operations reliably – key criteria for initialization, test, and debug.

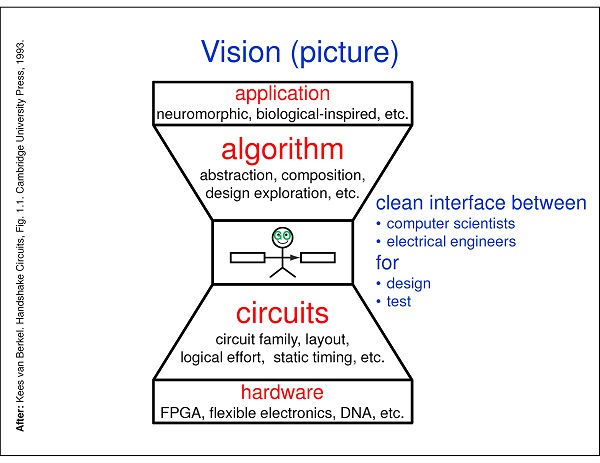

We are using Links and Joints as the interface between algorithmic programs and circuits. Networks of alternating Links and Joints are high enough to allow syntax-directed program translations and low enough to provide circuit implementations for different protocols and circuit families.